在今天的Ignite开发者大会上,微软发布了两款专为其数据中心基础设施设计的新芯片:Azure Integrated HSM和Azure Boost DPU。

这些定制设计的芯片计划在未来几个月内发布,旨在解决现有数据中心面临的安全性和效率差距,进一步优化其服务器以应对大规模 AI 工作负载。微软此前已发布Maia AI 加速器和 Cobalt CPU,这是该公司全面战略的又一大步,该战略旨在重新思考和优化其堆栈的每一层(从芯片到软件),以支持先进的 AI。

入局DPU

过去几年,CSP厂商都纷纷入局自研了DPU,但作为全球*的厂商,微软在这方面非常淡定,过去多年一直坚持在使用基于FPGA打造的产品。但今天,他们终于披露了*自研的DPU产品。在微软看来,数据处理单元 (DPU) 针对需要以网络线速处理大量数据的任务进行了优化。可以作为以数据为中心的设备(如存储系统)的独立处理器运行。

据介绍,公司*DPU名为Azure Boost DPU ,旨在高效、低功耗地运行 Azure 以数据为中心的工作负载。通过将传统服务器的多个组件整合到一块硅片中。Azure Boost DPU 将高速以太网和 PCIe 接口以及网络和存储引擎、数据加速器和安全功能集成到一个完全可编程的片上系统中。

微软同时表示,Azure Boost DPU 专为 Azure 基础架构构建,是一种软硬件协同设计,可运行自定义的轻量级数据流操作系统,与传统实现相比,可实现具有更高性能、更低功耗和更高效率的敏捷平台。

例如,与现有 CPU 相比,微软预计 DPU 运行云存储工作负载的功耗将降低三倍,性能将提高四倍。此外,基于 DPU 的系统添加了一个自定义应用程序层,该层利用 DPU 紧密集成的数据压缩、数据保护和加密引擎,为安全性和可靠性树立了新标准。

微软在分享的博客文章中写道:“Azure Boost DPU 专为 Azure 上的横向扩展、可组合工作负载而设计,可为其云基础设施提供跨存储、网络、加速等方面的效率。”

谈到为何推出这颗DPU,微软在博客文章中指出,作为优化 Azure 基础架构的全面方法的一部分,公司正在努力消除阻碍实现客户价值的基础架构限制 — 无论是性能瓶颈还是资源限制。我们正在从硅片到系统再到软件的每个层面进行创新,以增强基础架构的安全性、效率、性能、灵活性和规模。

微软认为,在云和人工智能时代,通过网络安全可靠地存储和移动大量数据已成为重大挑战。几年前,公司看到需要一种新的以数据为中心的处理器架构来补充大型数据中心使用的 CPU 和 GPU,以应对这些挑战。传统的 CPU 架构非常适合通用任务,但在处理与数百万个网络连接相对应的高度复用的数据流时却显得力不从心。另一方面,GPU 专门用于人工智能工作负载的核心大规模矢量和矩阵计算,因此它们也不太适合以数据为中心的工作负载。

这些观察结果促成了一类新型硅片的开发,即数据处理单元 (DPU)。

关于这些DPU的基准测试,微软并没有透露太多信息。Azure Boost DPU 在哪些工作负载上更节能,与哪些现有硬件相比,它的速度究竟更快?微软同样没有透露,也没有提到 Azure 客户何时可以看到这些收益。

但我们可以知道的是,微软的Azure Boost DPU 可能起源于 Fungible,这是一家 DPU 制造商,微软去年 12 月收购了该公司。据报道,微软以约 1.9 亿美元收购了这家由前苹果和瞻博网络工程师创立的公司。收购后,Fungible 团队加入了微软的基础设施工程部门。

加码安全芯片

在推出自研DPU的同时,微软还发布了一颗新的安全芯片Azure Integrated HSM 。

对于云厂商有了解的读者应该知道,微软的竞争对手AWS 和 Google Cloud 也构建了自己的内部安全芯片。虽然AWS 的 Nitro 安全芯片和 Google Cloud 的 Titan“功能范围各不相同,但基本概念是相同的:为使用其服务的数百万用户提供完全安全的操作和数据环境。”

于是,微软全新的Azure Integrated HSM也亮相了。

据介绍,这是一款全新的内部云安全芯片,它允许将签名密钥(基本上是数字加密签名)和加密密钥(用于加密数据的位串)包含在安全模块中,“而不会影响性能或增加延迟”。微软指出:“从明年开始,Azure Integrated HSM 将安装在微软数据中心的每台新服务器上,以增强 Azure 硬件集群对机密和通用工作负载的保护。”

Azure Integrated HSM 是微软继Pluton之后推出的第二款安全芯片,Pluton 是一款内置于英特尔、AMD 和高通处理器中的面向消费者的芯片。这也是该公司对其云竞争对手专有解决方案的回应。

定制芯片可以提高安全性,但并不是*的。2020 年,研究人员 发现 Apple 的 T2 安全芯片中存在一个“无法修复”的漏洞,这可能会让 Mac 面临该芯片旨在防范的威胁。微软没有提供有关 Azure Integrated HSM 漏洞测试的详细信息,但希望随着芯片的临近发布,微软会提供详细信息。

在备受瞩目的黑客事件和政府严厉批评报告曝光后,微软首席执行官萨蒂亚·纳德拉声称,安全现在是公司的首要任务。

根据微软的在一篇博客中所说,Azure Integrated HSM 旨在满足严格的联邦信息处理标准 (FIPS) 140-3 加密模块 3 级安全要求。Azure Integrated HSM 可在密钥和安全资产使用过程中保护这些资产。Azure Integrated HSM 具有专用的硬件加密加速器,可在加密、解密、签名和验证操作仍在集成 HSM 范围内时执行这些操作。

微软表示,典型的云 HSM 服务是网络上的集中式资源,可由云租户配置以向其各自的工作负载提供密钥服务。虽然这些模型提供了强大的密钥保护,但它们很难像其他资源(如计算)那样灵活地扩展。此外,当工作负载需要使用其密钥时,它们要么在调用网络连接的 HSM 服务时产生网络往返延迟,要么在其密钥策略允许的情况下,工作负载可能会请求从 HSM 释放其密钥并将其导入其本地环境。当密钥从 HSM 释放并导入工作负载环境时,提供的安全保护可能会低于 FIPS 140-3 3 级。

Azure Integrated HSM 则消除了在增加远程 HSM 服务的网络往返延迟与寻求从远程 HSM 释放密钥之间的传统权衡。作为安全绑定到工作负载环境的服务器本地 HSM,Azure 集成 HSM 为机密和通用虚拟机和容器提供本地附加的 HSM 服务。这提供了业界*的使用中密钥保护的优势,而没有往返网络连接 HSM 调用的延迟缺点。

微软安全副总裁 Vasu Jakkal 也在一篇文章中写道:“在当今快速变化的威胁形势下,受全球事件和人工智能进步的影响,安全必须是首要考虑的问题。”“新的攻击方法挑战了我们的安全态势,迫使我们重新思考全球安全社区如何保护组织。”

定制带HBM的CPU

在发布了两颗in-house的芯片以外,微软这次大会还披露了一颗由AMD定制的,带有 HBM3 内存的EPYC CPU。

微软表示,对于许多 HPC 客户来说,标准服务器设计的内存性能已成为实现所需工作负载性能(洞察时间)和成本效率的*障碍。为了克服这一瓶颈,微软和 AMD 合作开发了具有高带宽内存 (HBM) 的定制第四代 EPYC 处理器。

据介绍,在新推出的Azure HBv5 VM 虚拟机中,带有四个上定制的处理器,加上所有附加功能,单个 HBv5 VM 可提供 450GB HBM3、352 个 Zen 4 核心(时钟频率高达 4GHz),以及普通 Epyc CPU 上可用的两倍 Infinity Fabric 带宽。不过,SMT(超线程)已被禁用。这些 VM 还具有 800Gb/s 的 Nvidia Quantum-2 InfiniBand 用于网络交换。

按照tomshardware所说,四个 CPU 共有 352 个核心,每个 CPU 有 88 个核心,不过处理器上的每个核心可能并非都暴露给虚拟机。每个 Zen 4 CCD 都有 8 个或 16 个核心,具体取决于它是 Zen 4 还是 Zen 4c;定制 CPU 要么使用 11 个 Zen 4 CCD,要么使用 6 个 Zen 4c CCD,其中一个 CCD 上的 8 个核心被禁用。更可能的是,CPU 有 96 个功能齐全的核心,其中 8 个保留用于操作虚拟机,可能充当编排或虚拟机管理程序的角色

得益于这些配置,能提供近7 TB/s ( 6.9 TB/s)的内存带宽。相比之下,与最新的裸机和云替代方案相比,这高出 8 倍,比 Azure HBv3 和 Azure HBv2(带有 3D V-cache“Milan-X”的第三代 EPYC 和第二代 EPYC“Rome”)高出近 20 倍,比接近硬件生命周期末期的 4-5 年 HPC 服务器高出 35 倍。

下图显示了 Azure HBv5 VM 与前几代 Azure H 系列 VM 的 STREAM 性能比较。

外媒tomshardware表示,这款“定制”的 AMD CPU 可能也不是那么定制,因为它听起来很像去年传闻的 MI300C 芯片。在他们看来,这款 CPU 预计本质上是 MI300A APU,但专门配备 Zen 4 CCD 而不是 CDNA 3 显卡,从而允许使用带有 HBM3 的 96 核 CPU。MI300A 的 CPU 核心时钟频率高达 3.7GHz,与用于 HBv5 的 CPU 相差不远,这表明定制的 Azure 处理器和 MI300C 可能是同一款。

然而,尽管 HBv5 CPU 在技术层面上可能不是定制的,但它仍然是微软的专属 CPU。“它仅在 Azure 上可用,”微软工程师 Glenn Lockwood 在Bluesky上回答一位用户想知道 AMD CPU 是否会成为常规 Epyc CPU 时如是说。

值得一提的是,如上所说,在这颗CPU中,他们集成了常见于GPU的HBM。

针对这个做法,AMD 内存工程师 Phil Park 表示,为什么我们没有早点看到EPYC+HBM?因为EPYC 一直专注于大批量市场,这就是为什么你看不到超过 2 个插槽的 EPYC。Park 在Bluesky上发帖称。“你不能换掉你的 DDR5 控制器,添加 HBM 控制器/堆栈,然后就完事了。HBM 强制某些设计选择(例如,每个 HBM3 堆栈都需要 16 个 64 位通道)。”Park接着说。

换而言之,考虑到灵活性,所以我们很少在CPU中看到HBM。因为如果你使用 了HBM,您无法升级容量,也无法获得具有更少通道的低成本版本。而且,通常CPU 不需要那么大的带宽。

不过,我们也必须承认的是,英特尔其实早就已经推出了基于 Sapphire Rapids 的 HBM 注入 CPU,称为 Xeon Max,用于Aurora 超级计算机,并且也普遍可用。

投资芯片初创公司

在自研和定制芯片以外,微软还通过投资芯片公司,扩展其芯片布局。例如,近年来投资的,叫板英伟达的芯片初创公司d-Matrix,就是其最新杰作。

d-Matrix 由 Sid Sheth 和 Sudeep Bhoja 于 2019 年创立,总部位于加利福尼亚州圣克拉拉。该公司已筹集 1.54 亿美元,并得到 25 多家公司的支持。新加坡淡马锡是最新 B 轮融资的领投方。微软的风险投资基金 M12 也是投资者之一。

据该公司所说,d-Matrix 正在利用内存计算 (IMC) 技术与芯片级横向扩展互连,构建一种进行数据中心 AI 推理的新方法。公司也将利用创新的电路技术、ML 工具、软件和算法攻克了内存计算集成的物理问题;解决了内存计算集成问题,这是 AI 计算效率的最终前沿。

近日,d-Matrix 也终于推出 Corsair,用于无需 GPU、HBM 的 AI 推理,直接叫板英伟达。从设计上看,Corsair 采用行业标准的 PCIe Gen5 全高全长卡外形,通过 DMX Bridge 卡连接成对的卡。每张 Corsair 卡都由多个 DIMC 计算核心驱动,具有 2400 TFLOP 的 8 位峰值计算能力、2GB 的集成性能内存和高达 256GB 的片外容量内存。DIMC 架构可提供 150TB/s 的超高内存带宽。

按照他们所说,这是全球最高效的数据中心 AI 推理平台。在单台服务器中 Llama3 8B每秒处理 60,000 个tokens,每个tokens的延迟为 1 毫秒。因此,该公司声称,与 GPU 和其他替代方案相比,Corsair 提供了性能、能源效率和成本节省。

众所周知,使用生成式人工智能(称为推理处理)是一项内存密集型操作。它需要大量内存,也需要非常快的内存,但两者兼顾确实很难。与处理器位于同一芯片上的 SRAM 内存比,堆叠在 GPU 或加速器上的高带宽内存快一个数量级。但 SRAM 要小得多,因此很难处理可能具有数千亿个参数的模型。d-Matrix 有一个独特的解决方案,可以赢得这场拉锯战。

d-Matrix 采用混合内存方法,似乎能带来出色的效果,使用 SRAM 作为“性能内存”,使用更大的 DRAM 存储器作为“容量内存”。性能内存用于需要低延迟交互的在线操作,容量内存用于离线工作。

Corsair 还配备了高达 256 GB 的片外容量内存 (DRAM),可在不需要低延迟的离线用例中支持 Gen AI 工作负载。在容量模式下,Corsair 支持大型模型、大型上下文长度和大型批处理大小。例如,具有 8 张 Corsair 卡的服务器可以容纳超过 1 万亿个参数的模型。

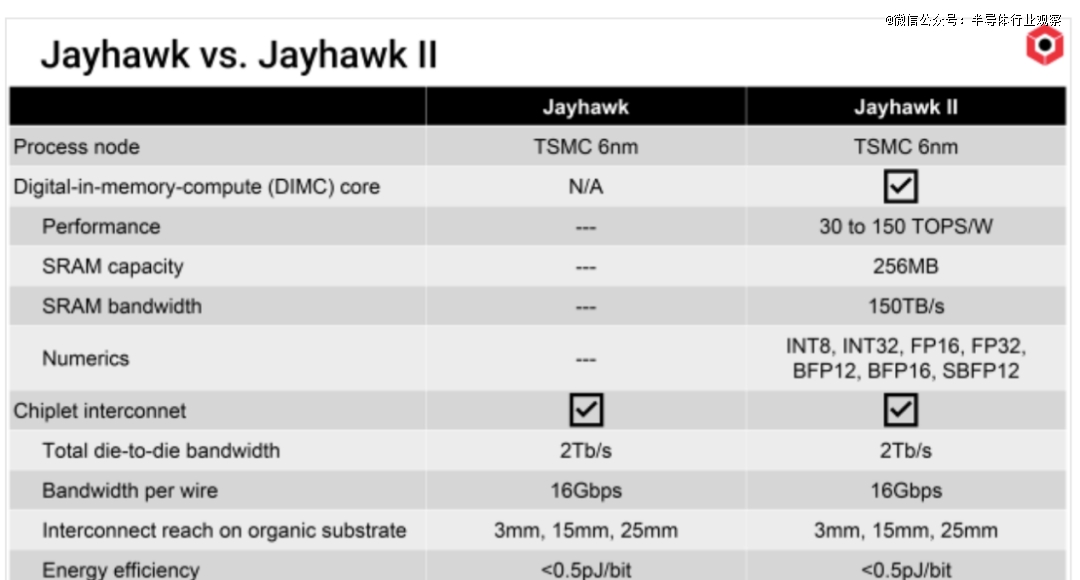

据介绍,Corsair 基于采用 6nm 制造工艺技术实现的 Nighthawk 和 Jayhawk II 芯片。Nighthawk 包含四个神经核心和一个 RISC-V CPU。

相关信息显示,d-Matrix的每个 Jayhawk II 芯片组都包含一个 RISC-V 内核来管理它,32 个 Apollo 内核(每个内核有 8 个并行运行的 DIMC 单元),256 MB SRAM,带宽为 150 TB/s,两个 32 位 LPDDR 通道和 16 个 PCIe Gen5 通道。内核使用带宽为 84 TB/s 的特殊片上网络连接。每个带有 32 个 Apollo 内核/256 个 DIMC 单元和 256 MB SRAM 的芯片组可以以超过 1 GHz 的速度运行。

据TechInsights称,每个 DIMC 核心每周期可执行 2,048 次 INT8 乘法累加 (MAC) 运算。每个核心还可以使用行业标准 (INT8、INT32、FP16、FP32) 和新兴专有格式 (块浮点 12 [BFP12]、BFP16、SBFP12) 处理 64 × 64 矩阵乘法。

如上所述,该芯片已经配置为使用数字内存计算(DIMC)和包括块浮点(BFP)在内的各种数据类型来解决大模型推理。

据d-Matrix此前介绍,这个新型 DIMC 架构通过紧密集成计算和内存打破了内存壁垒。片上内存计算复合体的集成性能内存以其 150 TB/s 的超高带宽实现了快速令牌生成,比目前可用的 HBM-3e 高出一个数量级。在性能模式下,Gen AI 模型可适应性能内存,与使用 HBM 的替代方案相比,可实现高达 10 倍的交互延迟。

同时,d-Matrix 也是业内首批原生支持块浮点数值格式的公司之一,该格式现已成为一种称为微缩放 (MX) 格式的 OCP 标准,可提高推理效率。分层内存创新与 d-Matrix 的 Aviator 软件堆栈集成在一起,为 AI 开发人员提供熟悉的用户体验和工具。

d-Matrix 联合创始人兼首席执行官 Sid Sheth 表示:“我们预见到了transformers和生成式人工智能的到来,并成立了 d-Matrix 来解决我们这个时代*的计算机会所带来的推理挑战。首创的 Corsair 计算平台为具有多个用户的高交互性应用程序带来了极快的tokens生成速度,使 Gen AI 具有商业可行性。”

d-Matrix 断言,推理软件代理(agentic AI)和交互式视频生成的出现是 AI 能力和功耗的下一步提升,从而引发对改进处理架构的需求。

Corsair 利用chiplet 封装以及内存和计算的紧密集成,而 d-Matrix 则提供 Aviator 软件堆栈来支持 AI 开发人员。

我们也知道,访问额外性能内存容量的另一种方法是通过扩展,将许多 Corsair 集群在一起。扩展是使用基于芯片的架构实现的,该架构具有 DMX Link 以实现高速节能的芯片到芯片连接,以及 DMX Bridge 以实现卡到卡连接。