上周,众多芯片领域的重要人物齐聚旧金山,为了参加全球最重要的芯片领域会议ISSCC 2023。今年是第七十届ISSCC会议,其主题是“半导体电路设计创新70年”(Building on 70 years of innovation in solid-state circuit design)。过去的70年是半导体芯片行业突飞猛进的70年,而到了今天,芯片领域下一个创新的机会在哪里呢?在今年ISSCC的主旨演讲(Plenary)以及会议发表的论文中,我们认为核心关键词就是“系统级创新”(system inovation)。

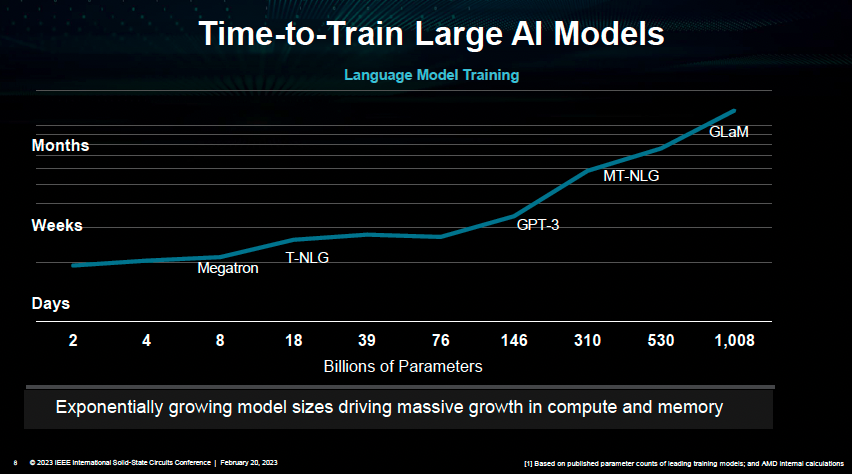

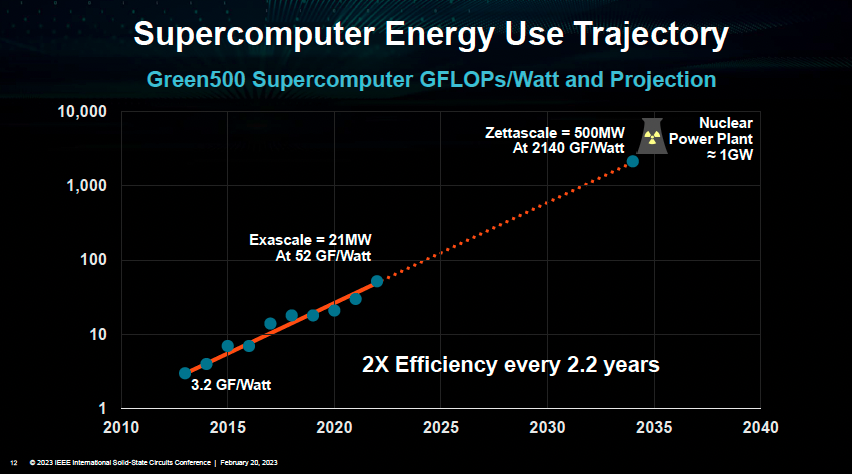

在AMD的CEO Lisa Su带来的主旨演讲“Innovation for the next decade of compute efficiency“(下一个十年计算效率的创新)中,Su提到了AI应用的突飞猛进,以及它给芯片带来的需求。随着以ChatGPT为代表的大语言模型(LLM)逐渐流行,AI模型的参数量指数级上升,而相应地对于计算芯片和内存的需求也在快速提升,但是目前芯片的效率并不足以满足模型的需求。根据目前计算效率每两年提升2.2倍的规律,预计到2035年,一个超级计算机需要的功率可达500mW,相当于半个核电站能产生的功率。显然,为了满足这样的计算需求,计算效率的提升需要远远超过每两年2.2倍,而为了实现这样的效率提升,系统级创新是最关键的思路之一。

在另一个由欧洲最著名三个的半导体研究机构IMEC/CEA Leti/Fraunhofer带来的主旨演讲中,系统级创新也是一个核心关键词。该演讲中提到,随着半导体工艺逐渐接近物理极限,新的应用对于芯片的需求也必须要从系统级考虑才能满足,并且提到了下一代智能汽车和AI作为两个尤其需要芯片从系统级创新才能支持其新需求的核心应用。

什么是系统级创新?

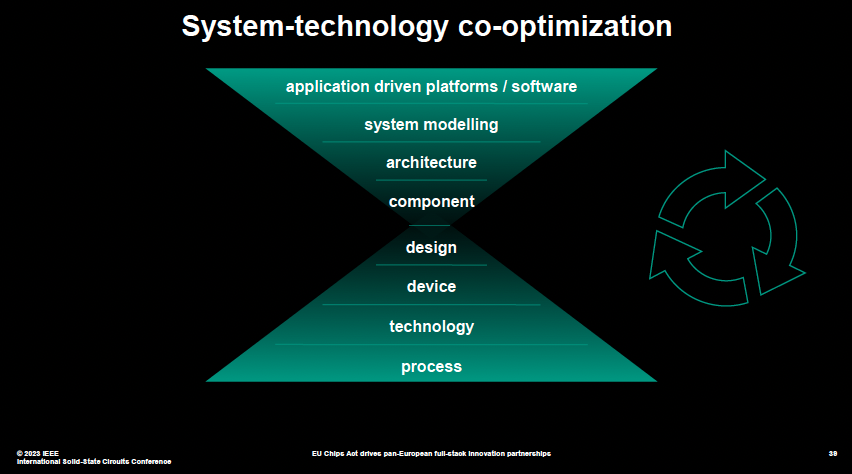

我们看到,系统级创新在本届ISSCC最重要的主旨演讲中被反复提起,那么什么是系统级创新呢?目前的共识是,系统级创新就是从整体设计的上下游多个环节协同设计来完成性能的提升。在系统级中,上游技术包括应用软件,算法,系统架构,元器件需求等,而这些上游的需求最后会反映到芯片的需求中,包括芯片的设计,半导体器件的设计,以及半导体工艺的设计等。

在过去的设计中,性能提升往往只是体现在一个维度中,例如电路设计的成功标准是数字电路时钟频率能不能跑得够快,模拟电路能不能带宽做到更大等等。而在系统级创新中,性能提升不仅仅是由该技术层面的设计改善实现,更重要是由上游应用、算法和系统革新并且由电路、器件和工艺层面的设计满足这些需求,来完成整体性能的提升。

Lisa Su在演讲中给出了一个系统级创新的一个经典案例,就是在人工智能模型算法层面通过优化从而可以使用一些创新的数制(例如16位浮点数BF16或8位浮点数FP8),同时在电路层面通过对这些算法层面优化给予支持,最终实现计算层面数量级的效率提升。相比传统的32位浮点数(FP32),新的BF16可以提升10倍以上的计算效率,而FP8则可以将计算效率提升30倍之多。这也是系统级创新的威力:根据传统思路,如果电路设计仅仅停留在电路的维度,只是考虑如何进一步优化FP32计算单元的效率,无论如何也难以实现数量级的效率提升。这也是为什么在新应用对于芯片性能提出非常激进的性能需求的时候,芯片行业需要从系统级的思维来满足这样的需求的原因。

作为系统级创新支柱的半导体技术

如前所述,半导体芯片的设计需要考虑系统级创新,才能满足新的应用对于芯片性能提升的需求。从另一层面,在这样的系统级创新中,有一些重要的半导体技术将会成为核心的支撑,因此在系统级创新成为核心技术演进动力的今天,这些半导体技术将会变得格外重要。

我们认为,系统级创新意味着整体芯片系统会变得更加复杂:这里的复杂意味着系统中会有更多的芯片(这也包括了把一块大芯片拆分成多个小的芯片粒),因此这就需要能以一种灵活的方式支持这样的多芯片系统,同时能提供性能和效率的显著提升。一旦半导体技术能提供这样的平台来支持这样的复杂系统,那么系统级设计就有了更大的设计空间,从而为系统级创新提供强有力的支持。

对于这样的复杂芯片系统提供高效支持的半导体技术首先是高级封装技术。使用高级封装技术,可以把复杂芯片系统以高效的形式集成在一个封装内,并且提供非常高的通信带宽,因此可以为系统级芯片创新提供支持。例如,高级封装可以把传统的片上缓存(cache)和处理器芯片以芯片粒的形式集成在一起,这样就大大减少了半导体工艺对于cache容量的限制,从而为系统设计提供了更大的设计空间,而这样的设计(3D V-Cache)已经被证明可以显著改善处理器的性能并且AMD已经在产品中使用。在未来,我们可望会看到更多的设计。

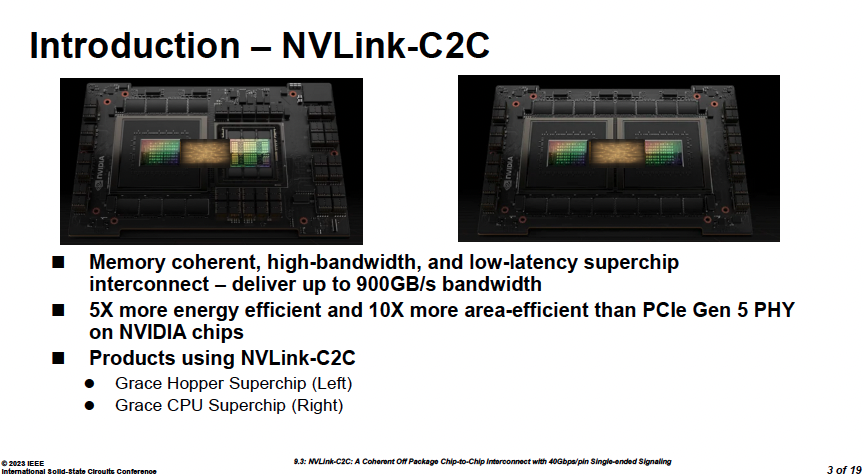

另一个与之相关的重要技术是IO接口技术,即能够进一步改进芯片之间互联的传输速度和效率。在Lisa Su的主旨演讲中,除了高级封装可以提升封装内芯片数据互联带宽之外,另外一个重要的维度是中长距离数据互联,用于在多个芯片系统之间以及在多台服务器之间高速高效地传递数据。这样的IO接口技术的演进可以大大减少系统中各个组件之间互相通信的开销,从而实现高效率的复杂芯片系统。在中距离(芯片之间)的数据互联角度,超高速SerDes技术将会成为未来的重要支撑技术。在今年的ISSCC上,Nvidia也发布了其用于芯片封装间互联的NvLink-C2C技术,可以实现高达40Gbps/pin,并且已经用在了其下一代GPU系统(Hopper)中,可见数据互联技术的重要性已经成为了芯片巨头的共识。

而在长距离互联上,光互联技术可望会成为技术演进的主要方向,其传输距离可达10m到2km,并且传输能量开销可以很低(<1pJ/bit)。在这个领域,需要把光传输收发模组和计算芯片很紧密地集成到一起(例如使用co-packaged optics技术),未来我们预计在技术方面也会有较快的演进。

综上,我们认为系统级创新已经成为了芯片行业性能提升的主要动力。系统级创新既包括了考虑系统上游(如算法和应用)的电路设计以实现性能和效率数量级的提升,也包括了新的半导体技术平台(如先进封装和IO技术)以为系统设计提供更多的设计空间。系统级创新为芯片提供的新机会值得我们期待。