1

简 介

半导体技术节点中的传统尺寸缩放是通过缩放金属间距(MP)和接触多晶硅间距(CPP)来实现的。在先进的CMOS技术节点(低于10nm)中,金属半间距已扩展到非常窄的尺寸(低于20nm)。在这些金属线宽处,由于金属丝的尺寸效应(如表面和晶界散射)的增加,金属的电阻率显著增加。电阻率的增加加剧了IR压降问题,并已成为亚5nm CMOS技术节点高性能设计的一个重要瓶颈。为了确保较低的IR压降,设计者经常被迫权衡信号路由资源,以构建更精细、更鲁棒的电网。作为亚5nm CMOS节点的技术助推,学者们提出埋入式功率轨(BPR)以实现标准单元面积缩放并降低IR压降问题。在该技术中,电源轨(例如VDD、VSS)埋在硅衬底内,并通过特殊通孔分接,以连接到电网(正面或背面)。具有高纵横比的BPR通过允许向晶体管输送功率的较低电阻路径来最小化IR压降。

除了芯片上的IR压降之外,由功率传输网络(PDN)的其他组件(如PCB、封装、C4凸块等)引入的寄生效应在瞬时电流尖峰条件下也会导致电压下降。这种片外压降可以通过增加片上去耦电容来降低。在埋入式轨道技术中,由于金属线布线在没有信号布线的基板下方,因此可以实现低电阻高纵横比功率轨。高纵横比有助于增加电源和接地之间的去耦电容,从而降低与自发电流尖峰事件相关的芯片外电压降。

在本文中,我们通过考虑三种PDN配置,对BPR和背面电网进行了整体评估,传统PDN配置为正面(FS)、带BPR的FS电力输送(FSBPR)和带BPR(BSBPR)的背面电力输送。使用具有代表性的64位CPU(如Arm1 Cortex1-A53 CPU)对这些配置进行评估,以量化对性能-功耗-面积(PPA)、片上IR压降、片外电压降和功率门控的影响。该领域的先前研究主要集中于物理设计或PDN建模。

我们研究的主要贡献如下:

1) 综合分析阐述了微处理器性能和不同PDN配置的片上IR压降之间的关键权衡。

2) 通过研究技术参数对背面PDN进行整体设计技术协同优化(DTCO),以优化片上IR压降和片外压降。

3) 评估功率门与BPR和背面电网技术集成所涉及的潜在挑战。广泛分析强调BPR对电网电阻的影响。

本文的结构如下:第二节介绍了BPR和背面电源的概念;第三节描述了各种功率传输配置;第四节介绍了CPU设计、片上IR压降、片外电压降和门控电网设计的结果;第五节是总结和结论。

2

技术概念

A.埋地电源轨

BPR可以在FinFET技术中实现。在鳍形成之后,BPR工艺模块首先在浅沟槽隔离(STI)中蚀刻一个空腔,该空腔延伸到硅中。随后是薄电介质阻挡层的原子层沉积(ALD),以将掩埋轨道与硅本体电隔离。然后用能够承受前端线(FEOL)热预算的金属(例如钌(Ru)或钨(W))填充空腔,促使进一步FEOL集成。实验证明BPR的电阻在30至50Ω/μm之间。

B. 背面功率传输

背面功率传输是一种独特的3-D集成技术,其中整个PDN集成在芯片背面。细间距微硅通孔(μTSV)将BPR连接到背面的PDN。在FS上进行处理后,将晶片减薄至500nm,并使用BPR金属作为蚀刻停止层从背面蚀刻μTSV。随后沉积背面金属层以将功率分配给C4凸块。

3

PDN配置

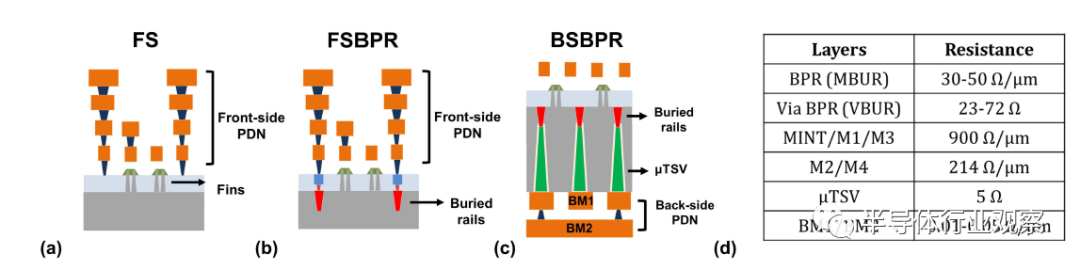

在本文中,我们探讨了三种不同的电源传输配置:1)FS,其中信号和功率网络在芯片的FS上[见图1(a)];2) FSBPR与FS相似,不同之处在于标准电池的电源轨道埋在衬底内[见图1(b)];和3)BSBPR,其中电源网络在芯片背面布线,但信号网络在芯片的FS上布线[见图1(c)]。

图1 (a)FS PDN示意图。(b)FSBPR示意图。(c)BSBPR示意图。(d)表中展示了关键金属层的电阻。

A.BPR标准电池设计和金属互连

为了评估BPR的系统级影响,IMEC的iN6技术节点(相当于IRDS 3 nm)中的标准单元设计了BPR和不包含BPR。FS配置通过使用标准单元库的常规设计流程实现,无需BPR。FSBPR/BSBPR配置使用实现BPR技术的标准单元库,以及修改后的标准单元布局、技术库交换格式(LEF)和捕获BPR效果的互连RC文件。该技术节点中的标准单元为六轨高,四轨预留用于布线,两轨预留用于电源轨。虽然BPR可以使标准的单元高度缩放到五个轨道,但这项工作只考虑六个轨道高的单元,这使得能够从IR下降的角度公正有效地评估埋轨。iN6技术有一个14金属层互连堆栈:M1–M13和MINT(iN6技术节点中用于局部布线的中间金属层),互连节距代表约3 nm技术节点,具有连接C4凸块的单个再分布层(RDL)。FSBPR和BSBPR配置具有额外的埋入金属层(MBUR)。图1(d)显示了一些细间距金属互连层的电阻。

B.FS/常规PDN

在FS配置中,电源线位于MINT金属层(M1以下的*后端(BEOL)金属层)上。小的MINT MP(~22 nm)使得电阻约为900Ω/μm的高电阻电源轨,导致CPU设计中出现IR下降热点,这将在后续章节中讨论。为了研究PDN设计对性能/IR压降的影响,考虑了三种不同的PDN设计,增加了电网密度(PDN1最稀疏,PDN3最密集)。表I给出了FS配置的每个PDN设计的规范。三种PDN设计中的每一种都有四个金属层(M1、M2、M5和M6)用于实现局部信号路由,这四个金属层上的电网仅限于通孔结构(这些层上没有金属条)。

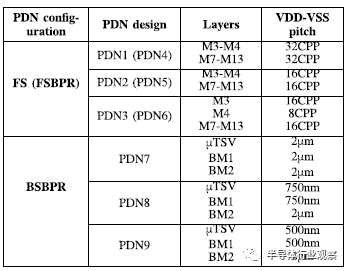

表IPDN配置规范(CPP=45 nm)

C.带埋地轨道的FS PDN

标准电池的电源轨在FSBPR配置中使用MBUR层(埋置金属层)。BPR的访问仅限于特定的“分接”点,在该点,电介质被蚀刻以创建特殊的通孔(通过VBUR掩埋)。这些特殊的通孔嵌入在设计中精心放置的专用抽头单元中,抽头单元消耗额外的面积并阻碍设计中标准单元的放置。因此,抽头单元的放置是FSBPR设计中的关键设计约束。与FS配置类似,FSBPR配置考虑了三种PDN设计(PDN4–PDN6),如表I所示。

D.带埋地电源轨的背面PDN

BSBPR配置消除了FSBPR配置中所需的抽头单元的开销,它减少了FS上的布线拥塞,因为所有金属资源都可以专用于信号/时钟路由。然而,信号I/O必须与电源轨一起穿过芯片背面,才能最终连接到C4凸块。BPR和μTSV引起的附加寄生电容可以通过技术创新来补偿。近年来,由于实现低功耗芯片的巨大潜力,这种配置获得了关注。在本研究中,背面的PDN限于三个金属层(MBUR:掩埋金属,BM1:背面金属-1,BM2:背面金属-2)。如果设计规范要求,可以在背面添加额外的层。由于背面金属堆叠专用于电源接地布线,金属互连可以具有大的轨道宽度(>250nm),这可以显著降低栅极的电阻。μTSV间距减小,但这是以增加工艺复杂性为代价来实现的。为了研究μTSV间距对IR压降的影响,本研究中考虑了三种PDN设计,如表II所示。

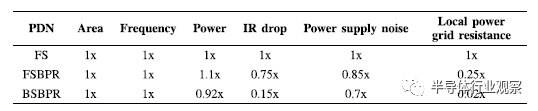

表II重要设计指标的比较

4

结果

A.CPU性能和IR压降

为了评估不同PDN配置的系统级影响,使用IMEC的iN6库实现了具有代表性的64位高效CPU(如Cortex-A53)的物理设计实现。这些设计具有单个功率域(VDD=0.7V),并在等面积条件下(管芯面积-150μm×150μm)进行比较。图2(a)显示了三种PDN配置的芯片功率与性能的关系。由于显著减少了路由拥塞,利用BSBPR配置的实现在整个设计频率范围内消耗的功率低于FS/FBSPR配置。相比之下,由于抽头单元产生的开销,FSBPR配置比FS配置消耗更高的功率。总体而言,对于1.4(标准化单位)的等频率,FSBPR的功耗比FS配置高10%,BSBPR的能耗比FS配置低8%。

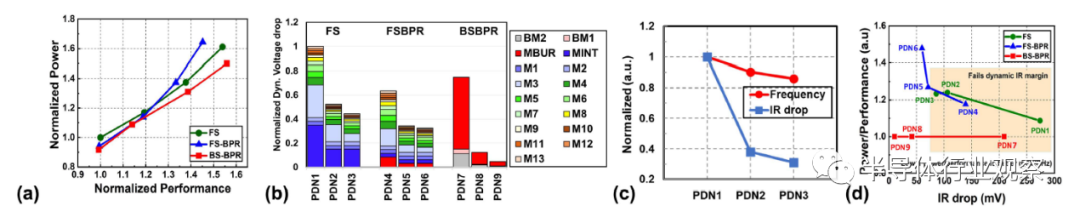

图2.(a)标准化的功率与性能。(b)PDN1-9的基于层的IR压降分布。(c)PDN1-3的频率和红外压降变化。(d)所有PDN配置的能量与动态IR压降。

Cortex-A53 CPU的放置和布线物理设计用于Cadence Voltus环境中的无矢量动态IR压降分析。图2(b)显示了九种PDN设计中每一种设计的IR压降的分层分布(见表I)。在FS配置中,高电阻局部金属层(MINT-M3)在具有32CPP节距的PDN1中贡献了约60%的IR压降。在具有16CPP MP的PDN2中,局部金属层中的显著IR压降降低到一半。通过仅将PDN3中的M4 MP降低到8CPP,IR压降进一步降低。更致密的M4 MP减少了高电阻M3金属层上的IR压降。在FSBPR配置中,电阻较小的MBUR层(30Ω/μm)取代了电阻较高的MINT层(900Ω/μμm)。在所有三种PDN设计(PDN4–PDN6)中,这将FSBPR配置中的总体IR压降下降约30%。BSBPR配置的IR压降强烈依赖于μTSV间距。尽管MBUR具有低电阻(30Ω/μm),但与电阻较小的背面金属层(BM1、BM2)相比,增加μTSV间距显著增加了MBUR层上的电压降。

图2(c)显示了FS配置中三种PDN设计的*实现频率和IR压降的变化。正如预期的那样,随着电网密度的增加,IR压降和达到的*频率逐渐降低。从PDN1到PDN3,性能下降30%,IR下降提高70%。当使用FSBPR配置实施时,PDN设计也观察到类似的趋势。图2(d)总结了本研究中考虑的所有PDN设计的功率/性能和IR压降之间的权衡。功率除以性能度量(mW/GHz)估计了在不同PDN配置中降低IR压降的能量损失。尽管从PDN1移动到PDN3时产生了增加的能量损失,但FS配置不满足IR压降目标。FSBPR配置虽然满足IR压降目标,但由于抽头单元的开销,它会经历更高的能量损失。相反,BSBPR配置完全解耦了这种折衷,并且不会产生任何能量损失以降低IR压降。

B.芯片外电压降分析

上一小节中给出的IR压降分析仅限于片上PDN。然而,芯片封装PCB寄生在瞬态电流尖峰事件期间会引起电源噪声(芯片外电压下降),我们通过模拟图3(a)所示的等效电路来估计电源噪声,这种电源噪声可以通过增加片上去耦电容来降低。

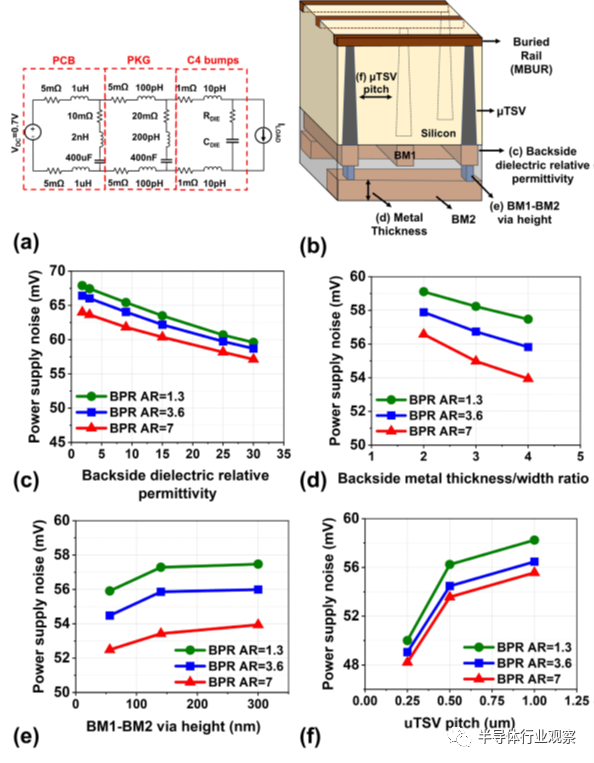

图3(a)芯片封装PCB系统的等效电路模型。(b)BSBPR中可能的优化说明。电源噪声随(c)背面介电相对介电常数、(d)背面金属厚度与宽度之比、(e)BM1-BM2通孔高度和(f)μTSV间距的变化。

与层间电介质(k~1.8)相比,BPR封装在相对较高的介电常数材料(硅:k~11.7)中,从而增加了去耦电容。掩埋轨的厚度也高于局部金属层(M1–M6),从而增强了侧壁去耦电容量。使用Synopsys Raphael RC提取引擎获得埋地轨道和PDN其余部分的电阻/电容。与FS配置相比,由于埋轨而增加的去耦电容使FSBPR中的电源噪声(*电压下降幅度)降低了17%。模拟是在考虑八核配置的情况下进行的,其中一核开关,其它核提供有用的去耦电容。在BSBPR配置中,可以独立优化背面的电网,以增加去耦电容并降低电源噪声。背侧电网的去耦电容可通过以下方式增加:

1) 增加背侧相对介电常数;

2) 增加背面金属厚度;

3) 减少连接背面金属层的通孔高度;和

4) 减少μTSV间距。

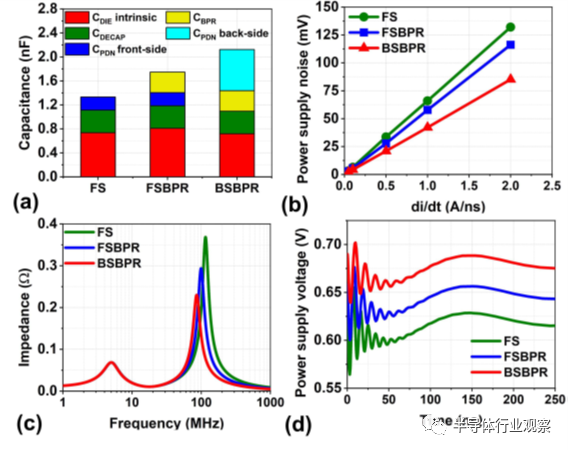

由于增加了信号到信号噪声耦合的风险,在FS/FBSPR配置中无法进行这些修改。因此,BSBPR配置提供了增加去耦电容和减少电源噪声(*电压降的幅度)而不影响信号完整性的独特机会。图3(c)显示了三种不同BPR纵横比下电源噪声随背侧电介质相对介电常数的变化。CMOS兼容的高k氧化物,如Al2O3(k~9)或HfO2(k~23)可以替代通常*的低k层间电介质(k~1.8)。通过将电介质相对介电常数从1.8增加到约25,电源噪声降低了12%。增加背面金属厚度会增加侧壁电容并降低电源噪声,如图3(d)所示。类似地,减小背侧金属层之间的通孔高度会增加BM1和BM2层之间的电容,如图3(e)所示。此外,减小μTSV间距会增加侧壁电容,并有助于降低电源噪声。如图3(f)所示,将μTSV间距从1减小到0.25μm可将电源噪声降低15%。总体而言,与FS和FSBPR配置相比,优化的BSBPR配置(介电常数=25,厚度/宽度比=3,通孔高度=140 nm,μTSV间距=250 nm)分别具有59%和21%的去耦电容。图4(a)显示了同轴PDN的各个组件的去耦电容贡献。图4(b)显示了瞬态电流尖峰事件的电源噪声随di/dt的变化。与FS和FSBPR相比,优化的BSBPR配置具有更低的电源噪声。在频域中,BSBPR的峰值阻抗移向较低的频率,峰值的幅度降低了34%,如图4(c)所示。图4(d)显示了用阶跃电流输入模拟的相应时域电压瞬态,其波形显示了FS、FSBPR和BSBPR配置的最坏情况,即动态IR压降(由于电网电阻导致)叠加电源噪声(由于芯片外电压下降导致)。

图4(a)解耦电容比较,突出不同组件的贡献。(b)电源噪声随阶跃输入电流变化率的变化。(c)芯片封装-PCB系统的阻抗曲线。(d)瞬态电流尖峰事件时的电压响应。

A.电源门实施

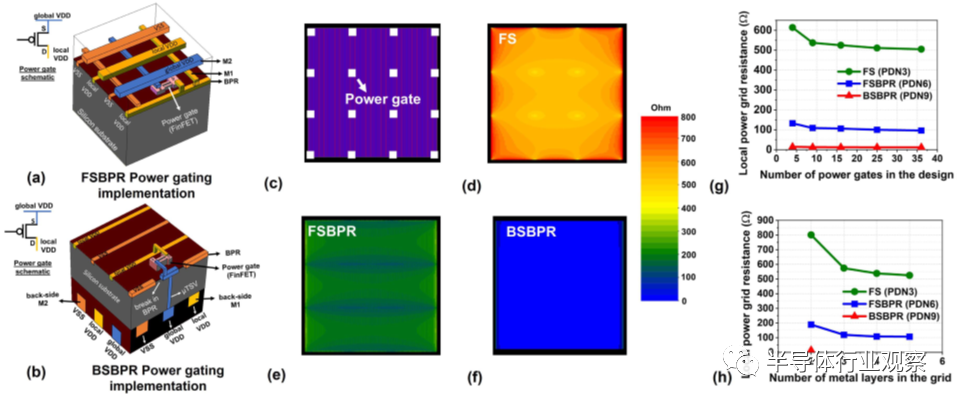

前两节中给出的片上IR压降和片外电压降分析未考虑设计中的功率门。然而,大多数现代SoC模块都包含功率门控,来将非活动内核消耗的泄漏功率最小化。在功率门控技术中,局部电网(或功率域)通过称为功率门的可切换晶体管连接到全局电网(主电源)。本节介绍BPR对采用功率门控技术的设计的影响。图5(a)和(b)分别说明了FSBPR和BSBPR设计的潜在功率门集成方法。为了清楚起见,图中省略了标准电池和BEOL金属互连。此外,全局VDD(主电源)、局部VDD(电源域)和VSS互连采用颜色编码,以匹配电源门示意图[见图5(a)和(b)]。在FSBPR配置中,电源门连接到BPR层上的局部VDD(而不是FS配置的MINT层)。为了便于这种连接,VBPR需要容纳在功率门的标准单元内。在BSBPR配置中,采用低电阻背面金属来实现局部和全局电网,以最小化IR压降。全局VDD通过背面金属和μTSV连接到电源门,由于μTSV需要BPR连接,因此可以拆分VSS BPR以创建一个孤立的全局VDD BPR岛,如图5(b)所示。然后,电源门的漏极连接到局部VDD BPR,后者通过背面金属向标准单元分配功率。

图5 示意图显示了(a)FSBPR功率门实施和(b)BSBPR功率栅实施。(c)电源网格图显示均匀分布的电源门,(d)FS、(e)FSBPR和(f)BSBPR PDN设计的有效电阻热图。(g)局部电网电阻随设计中功率门的数量的变化。(h)局部电网电阻随电网中金属层的数量而变化。

通常在功率门控的实现中,全局电网使用较高(BEOL)金属层(>M6或M7)设计,而局部电网使用较低金属层设计。高电阻局部电网对设计的总体IR压降有很大贡献。因此,在本节中,通过考虑局部电网电阻来研究埋地轨道对电源门控设计的影响。使用Cadence Voltus仿真环境分析局部电网电阻(FS、FSBPR和BSBPR设计)。功率门均匀分布在芯片区域[见图5(c)],并确定从功率门到每个标准单元的有效电阻。图5(d)-(f)显示了每种配置的紧密间距PDN设计的有效电阻热图:FS-PDN3、FSBPR-PDN6和BSBPR-PDN9。设计中所需的功率门数量取决于多个因素,如功率门电阻、芯片的工作频率、输入矢量等。因此,我们分析了峰值电阻(最坏情况下的标准单元)随设计中功率门数量的变化,如图5(g)所示。在这里,可以观察到一个重要的趋势,即电网的电阻会逐渐降低,并在每个配置的某个值处饱和。该最小限值由从最近通孔到最坏情况标准单元(位于两条VDD线之间的中间)的*金属层的电阻确定。由于MINT层的电阻很高(MINT电阻为~30×MBUR电阻[见图1(d)]),FS配置的局部电网电阻比FSBPR配置高4.5倍,比BSBPR配置低40倍。

在FS/FSBPR配置中,局部电网使用多达六个较低的金属层,其中大部分信号也被路由。如果局部电网电阻可以用更少的金属层满足期望的目标电阻,则可以专门为信号布线和全局电网布线分配额外的金属层。图5(h)显示了局部电网电阻随所用金属层数量的变化。BSBPR配置以单点显示,因为局部电网是使用两个可用的背面金属层设计的。在FS/FBSPR配置中,随着较高的金属层(具有较低的电阻)添加到局部电网,电阻会随之降低。正如预期的那样,FSBPR局部电网的电阻低于FS局部电网。为了满足所需的电阻目标(源自堆芯的活性),与FS配置相比,FSBPR电网可以使用更少的金属层。总体而言,由于BPR的载流能力增强,与FS配置的局部电网相比,FSBPR局部电网的电阻降低了大约4.5倍。由于BSBPR中使用超低电阻的背面金属来实现局部电网,因此与FS配置相比,紧密间距PDN9的电阻约为它的40倍。总的来说,低电阻BPR和背面金属层[见图1(d)]可以帮助缓解功率门控设计中的IR压降问题。

5

结论

本文中,我们采用BPR技术对PDN进行了全面的设计研究,考虑了不同可能的功率传输配置。通过64位高效CPU(如Cortex-A53)在低于5nm节点的物理设计实现,我们评估了系统级影响,对比了FS、FSBPR和BSBPR的功率、性能和IR压降表现情况。与FS配置相比,FSBPR和BSBPR配置可分别降低25%和85%的IR压降,从而轻松满足10%的IR压降目标。此外,提出了一种独特的方法来增强BSBPR配置的去耦电容,从而使电源噪声消耗比FS配置低30%。最后,分析了BPR对功率门控实现的影响。与FS配置相比,FSBPR和BSBPR的局部电网电阻分别为约4.5倍和约40倍。