5nm良率还在改善,3nm刚刚投产,而各大晶圆厂对于2nm的角逐已经进入白热化阶段。自从2021年,IBM发布了全球*2nm制造工艺,晶圆代工厂的2nm制程便像按了加速器般,整个芯片市场也将越来越多的精力向2nm转移。

01.抢跑2nm

在2019年,台积电便宣布启动2nm工艺的研发。据悉,台积电*2nm工厂——新竹N2厂正在进行土地取得作业,该厂将分四期建设,共建设4座12英寸晶圆厂,有望在2024年为苹果手机量产新一代芯片。

三星电子正计划通过在未来三年内打造2nm工艺来追赶台积电,目标是到 2025 年大规模生产先进的 2nm芯片,到 2027 年大规模生产 1.4nm 芯片。

自2021年提出IDM 2.0战略后,英特尔瞄准了从7nm至1.8nm的多代制程研发计划,计划一年一代推进,其中2024年将量产2nm制程,2025年量产1.8nm制程。

近日,包括丰田汽车和索尼集团在内的八家日本公司合作成立了一家芯片公司Rapidus,目标是在2030年前开发和生产2nm及以下半导体,日本政府将向Rapidus投资700亿日元(约4.93亿美元)加入八家企业支持者行列。

甚至欧盟委员会也提出数字化转型最新目标:到2030年,欧洲先进和可持续半导体的生产总值至少占全球生产总值的20%,生产能力冲刺2nm,能效达到今天的10倍。

先进制程的发展步伐正在加快,然而3nm技术还未完全成熟,为何已有多方开始布局2nm?

02.2nm如何成为香饽饽?

“到了未来的技术节点,间距微缩将减缓,硅晶体管似乎只能安全地微缩至2nm,而在那之后,我们可能就会开始使用石墨烯。”芯片制造的核心软件EDA巨头新思科技(Synopsys)研究专家Victor Moroz的这句话道出了2nm技术的重要性:2nm或许是硅芯片的最后一战。

除材料的革新外,2nm还涉及诸多埃米制程新工艺,占据了2nm的技术优势相当于*掌握埃米制程。台积电向来都是代工领域的先行者,这个节点对于台积电来说,已成为必争之地。

对于三星来说,2nm的研究进程在很大程度上受到了台积电的推动。苹果、英伟达、AMD、英特尔和高通向来都是先进技术产能的预定者,而在3nm制程中三星由于良率问题,导致订单都向台积电倾斜,一家独大带来价格攀升,此时若三星可以在2nm做出成绩想必会得到不错的收益。在产能面前台积电向来都是扩产大户,而EUV作为2nm制造最重要的设备,倘若不抓紧做动作,本就紧缺的EUV光刻机会不断交付到台积电手中,因此三星的步伐必须加快。

作为曾经的芯片制造巨头英特尔,在10nm及7nm上被台积电、三星拉开差距后,积极探索2nm及更先进制程的目的也是相对清晰,欲凭借先进制程的发展重回*地位,抢占2nm高地是其必然要迈出的一步。

再来看看2nm对日本的意义。对于日本来说,在全球疫情、缺芯、产业变革以及地缘博弈的冲击之下,各国力促半导体制造业回流、构建自主产业链的做法俨然已成为新的“较量场”。曾经在半导体领域辉煌又逐渐没落、在设备和材料领域依旧保持强大竞争力的日本半导体业自然想要重回半导体制造高位,把技术掌握在自己手中,这个入口就是2nm。IBM宣布正与日本政府支持的芯片制造商Rapidus合作,以帮助其制造目前*进的芯片。IBM是全球*发布2nm芯片制造技术的公司,此次两家公司联手也符合今年5月美日宣布合作生产2nm的信息。

各大厂商为争夺先进晶圆厂*的宝座,竞相把2nm作为先进制程竞争的拐点,然而2nm能否快速到来还存在较大疑问,毕竟2nm本身就是晶圆代工巨头的一场赌注,其中还有诸多难题仍待攻克。

03.高墙壁垒诸多

技术攻克难

在“2nm技术战”中,各家公司都分别在晶体管结构、光刻、材料、封装等进行核心技术创新竞争。

背面供电技术就是三星、英特尔以及台积电在2nm的共同选择,不过想将背面供电技术应用在批量生产中仍有很长的路要走。比如英特尔背面电源网络在晶圆加工过程中就存在诸多挑战,包括如何在下一代RibbonFET晶体管周围的狭小空间内图案化电接触特征,同时不影响其性能;以及怎样减薄背面硅,以可重复和可控的方式提供尽可能直接和低电阻的连接等一系列问题。

同样三星的MBCFET与台积电的GAAFET都是首次应用,相关的蚀刻及量测问题尚待克服,材料、化学品等也需要提升,新工艺在整个制造过程中都有可能由于各环节的不兼容带来诸多不稳定性。

光刻机陪跑

2nm工艺对EUV光刻机具有更高的依赖性,高数值孔径的EUV技术以及光源、掩模工具等技术均亟待优化。在光刻过程中,互联金属电阻的恶化、高精度沉积与刻蚀工艺的需求、电路的三维集成与封装技术的开发,都是2nm制程研发过程中必须解决的技术难题。

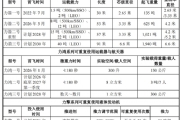

在光刻机的数量上,有日本专家做过推理和分析:在EUV层数方面,7nm+为5层,5nm为15层,3nm为32层,2nm将达45层。预计到2024年,启动2nm的大规模生产,2025年生产规模扩大,到时所需新EUV光刻机数预计为62台。而目前全球的EUV主要仰仗ASML,其一年的产能也只有50台左右,EUV设备的产量依然是一大难题。

3nm良率尚且偏低

目前可以量产3nm的只有三星和台积电两家,其中三星在今年6月就开始量产3nm,但由于良率问题一直让三星无法承接过多的订单。据悉,三星3nm制程良率不超过20%,为此三星表示正在与美国公司Silicon Frontline Technology扩大合作,希望通过对方的ESD(静电放电)预防技术,帮助三星晶圆厂改进前端(front-end)工艺和芯片性能。

在良率问题上,台积电的水准向来是比三星高出很多,据台媒消息,在台积电PPT一页内容上显示,其N3E 工艺进展良好,且平均良品率达到了80%以上。不过根据此前版本划分,N3是属于常规版本,而N3E(Enhanced) 原本是性能增强版,原计划是在N3量产后一年,2023年三季度之后才量产N3E。但根据目前不太理想的良率情况,N3E变成了精简版,规格缩水。看来台积电在3nm良率爬坡中也遇到了较大的阻力,因此才多次修正3nm蓝图。

3nm的良率尚且如此,何况2nm。

市场能有多大?

在前不久的IEDM会议上,Marvell公司公布了一些数据,援引IBS机构分析了各个工艺下芯片开发成本,其中28nm工艺只要4280万美元,22nm工艺需要6300万美元,16nm工艺需要8960万美元。后面的先进工艺开发成本就直线上涨,7nm需要2.486亿美元,5nm需要4.487亿美元,3nm需要5.811亿美元,而2nm工艺需要的开发资金是7.248亿美元,人民币约合50亿。

也就是说,如果某家公司想要自己研发一款先进工艺芯片,比如2nm处理器,不说设计周期要几年时间,光是投入的资金就得50亿元, 再加上台积电 3nm代工价目前已经突破2万美元 (约合人民币14.3万元),下游成本已大幅拉升。

在生产成本暴增下,芯片厂商势必会将成本压力转嫁到下游客户,但如今宏观经济前景黯淡,用户消费越来越理性,手机、PC市场持续下滑,面对如此敏感的价格有多少终端厂商敢贸然提价,又有多少消费者肯出钱买单?

04.2nm的发展是否操之过急?

先进制程虽好,但实现难度既艰难适用范围也有其局限性。在更广阔的领域,如工业以及军事领域,先进制程芯片反而没有成熟制程芯片可靠。如民用芯片、工业芯片和军用芯片所要求的正常工作的温度范围就有很大不同。民用级要求0℃~70℃、工业级要求-40℃~85℃、军用级要求-55℃~125℃,这仅仅是温度这一项指标,工业、军用级芯片还有抗干扰、抗冲击乃至航空航天级别的抗辐射等等要求,这些反而是更精密、更细小的先进制程芯片所难以达到的。

从应用领域来看,成熟制程已经能满足大多数电子设备以及国防设备的智能化需求;从技术水平看,成熟制程也比先进制程更加稳定、可靠且产业链生态更加完备;最后在经济成本上对比,对于量产规模不大、售价不高的中低端电子设备而言,成熟制程的芯片更具有性价比。况且多数应用领域并不需要用到更先进的2nm制程。对于一个复杂而庞大的芯片产业来说,制程并不是衡量芯片价值的*标准,良品率和产量同为重要。