据观察,硅芯片上的半导体元件数量呈指数增长,只有在达到某种极限时,才可能停止增长。这种趋势从每年每个芯片的组件数量翻一番放缓到每两年翻一番,中间翻一番的时间为18个月。这些观察结果通常被称为“摩尔定律”,这一基准基本上已成为微处理器行业无可争议但可能被误解的规则。

Sigmoidal模型(一种常见的S型函数曲线)已被证明与技术发展相符合,即使在反映晶体管性能的摩尔定律的背景下,也会随着技术的成熟而导致增长率下降。S曲线能够描述技术性能的增长。此外,这些模式在创新中得到普遍认可,包括技术生命周期和学习系统。简单logistic模型描述这一过程的能力可能是由于内在的技术和物理因素,以及制约复杂性不受限制地增加的经济力量。技术进步也被认为是一种准分形小波过程(quasi-fractal wavelet process),它将增长概念化为不同子过程的聚集。

事实上,许多复杂度和信息量不断增加的系统表现出不连续的多相趋势。Foster和Christensen提出了相连S曲线的假设。显然,他们假设的包括晶体管小型化在内的技术演变是不连续的,新的设计和工艺在“创新浪潮”的各个阶段中分布不均。由于限制因素,技术发展经常显示出带有饱和的趋势的更复杂的动力,这种模式也被报道于半导体性能当中。经验数据的逻辑成分分析和速率分析可以直接从数据中区分重要技术改进的时间,阐明晶体管小型化的主要趋势。尽管这些描述性模型可以洞察复杂系统的演化趋势,但它们并不用于解释提高技术性能本身的潜在机制。

大多数研究都接受了摩尔定律的假设,即计算机处理器复杂度(定义为每个芯片的单元数)指数翻倍。然而,晶体管计数的增加可能与芯片尺寸(芯片面积)的增加相耦合;也就是说,通过增加处理器的尺寸(面积或体积),可以向处理器添加更多的晶体管。最近,有人提出了晶体管密度的新定义,我们建议通过研究每单位面积晶体管数量的增长来重新分析处理器的发展,进而考虑芯片尺寸的变化。以*进产品密度为重点的分析可以确定包络函数,作为制造能力和技术的指标。本文测试了简单指数增长是否与历史时间序列数据一致,或者更复杂的模型是否能够更好地描述这一技术和经济现象。采用基于信息的参数优化和模型选择方法,以获得*的统计效率。

材料与方法

数据汇编

早期集成电路的数据来自仙童半导体国际公司,现代中央处理器(CPU)的数据来自英特尔公司(http://ark.intel.com)。为保持一致性,数据均来自在1959年至2013年之间。对于每个产品,记录CPU类型(台式机/移动设备)、发布日期、时钟频率(MHz)、制造工艺(nm)、晶体管数量和电路面积(mm²)的信息。自2014年以来,英特尔一直没有报告过有关较新CPU的技术信息,而高端产品的信息只能从各种在线非官方出版物中获得。

我们关注仙童和英特尔的数据,因为它们构成了最长的公开可用的时间序列,并且由于Gordon Moore最初担任仙童的研发总监,后来担任英特尔的执行官,并在1965年提出了他的定律。补充分析可能涵盖德州仪器公司的芯片,但Moore在德州仪器的对手Patrick Hagerty因1964年对逻辑门生产的十年预测而声名鹊起,因此这被证明是一个巨大的低估。IBM曾经是一家主要的芯片制造商,多年来一直将其大批量芯片生产外包给三星。三星于20世纪80年代开始生产,其竞争对手海力士(1983年)和台积电(1987年)也是如此。编制一个包括其他美国、欧洲和亚洲生产商在内的综合数据库将是一项艰巨的任务。

为了代表*进技术的发展趋势,每年最高密度的产品将说明该行业提高晶体管小型化的能力,从而得出CPU晶体管技术的制造能力和密度的时域包络。之所以选择这种方法,是因为在集成电路制造的最初几年中,数据仅适用于高端型号,即使实际生产中存在不太复杂的产品。更重要的是,在同一时间段内包括基于旧制造技术的产品将影响我们确定系统约束的能力。最后,这将为晶体管小型化趋势提供包络函数。本次调查中符合纳入标准的数据见S1表。

传统研究中,行业专家将每个芯片中晶体管数量的变化作为集成电路发展的变量进行跟踪。然而,这忽略了芯片尺寸的变化,因此并不能说明晶体管小型化的趋势。像Ferain等研究者一样,我们通过晶体管密度(定义为每单位面积的平均晶体管数量)来评估处理器的发展,从而聚焦小型化。

数学模型

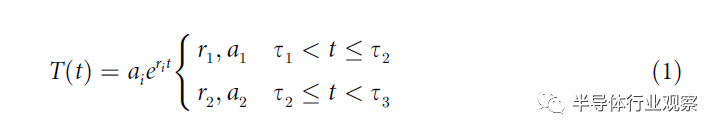

摩尔定律指出,晶体管的数量会一直增加,并且增长率可能在不同的时间发生变化;这在数学上与分段指数函数一致:

其中T是晶体管密度变量,生长阶段用i表示。生长速率常数(ri)包含了晶体管演化(τi)不同阶段的研发资源、制造技术和其他因素。半对数变换将等式(1)线性化,倍增时间的计算非常简单(t2=ln[2]/ri)。利用广义多元逻辑模型(generalized multilogistic model)来描述连续的技术发展浪潮(n),能够在包含约束因素的条件下描述其发展动力和趋于饱和的发展趋势,从而建立更复杂的处理器演化模型:

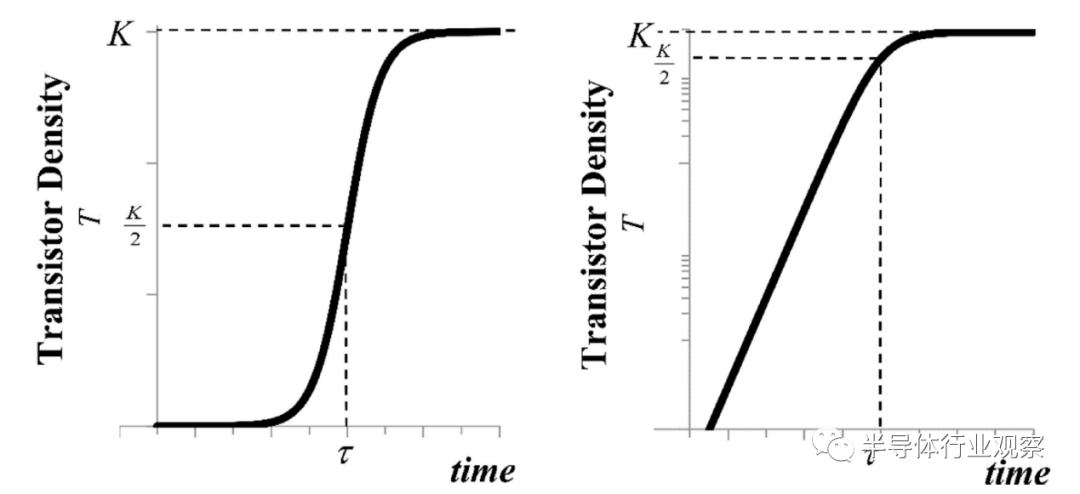

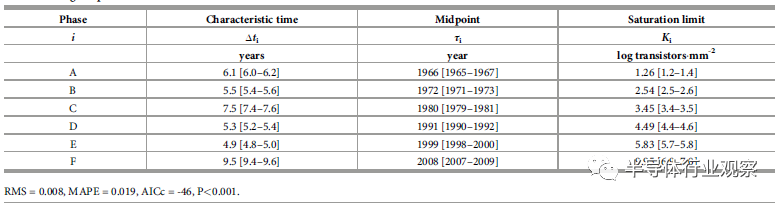

它有两个形状参数:每个生长阶段(i)的固有生长速率常数(ri)和饱和水平(Ki)。“特征时间”(Δti=ln[81]/ri)表示系统从10%饱和增长到90%饱和的时间。中点(τi)是一个位置参数,确定趋势达到半饱和时拐点的时间。它将曲线划分为凹增长模式和凸增长模式,模型渐近收敛到饱和值(图1A)。该模型的优点是,它能够描述一个系统的快速发展趋势,然后是成熟和饱和。在这种情况下,可以对晶体管小型化能力进行建模,其中r和K可能随时间而变化。log10转换后,逻辑函数不再呈S形。与指数模型不同,指数模型在整个范围内是线性的,因为指数部分在低密度下主导逻辑的行为(图1B)。单个S形生长趋势可分解为其组成曲线,这些曲线之后被线性化:

式中,对于每个生长阶段i(假设T<Ki),F=T/Ki,新标度可近似为生长曲线的百分比。

图1.时间相关logistic模型的一般形状与半对数变换后的曲线对比。A) 线性尺度上的logistic模型。B) logistic模型的半对数变换。注意函数初始阶段的近似指数行为。显示了中点半饱和点(τ)和渐近饱和点(K)。

参数估计、统计分析和模型选择

非线性拟合算法的初始参数值可以直接从估计数据中获得。有一种模式识别算法可以用于检测三个数据点(r>0.35 yr-1)之间的斜率显著增加后减小,随后斜率在至少连续四年的跨度内接近水平(t2<=0.5 yr),优先考虑这种稳定状态。在每个间隔结束时确定饱和点(K)。由于logistic模型在T<<K时收敛于指数模型,因此根据拐点之前log n转换数据的斜率计算r的*估计。为了描述增长率的变化,可以使用有限差分法(d2T/dt2)近似数据的加速度特性。当二阶导数从正到负交叉时,将观察到加速度变为负的拐点。然而,该分析增加了结果中的噪声,因此执行平滑滤波以增加信噪比。为了确认增长率中多个峰值的区分,算法上使用软件包Automatic Maxima Detection来识别嵌入数据中的变化率峰值,以确认这些结果。这将确定数值积分的最小初始估计,并将数据拟合到数学模型中。

然后使用基于模拟退火蒙特卡罗的遗传算法获得优化的参数值。简言之,从随机生成的参数集构建理论曲线集,并根据似然函数为每个拟合给出一个拟合分数:

式中,L是假设在正态分布(θ)中观察剩余(xi-X)的可能性,xi是时间i的数据点,X是n个数据点的期望值。然后将具有最小值(*拟合)的拟合子集的参数空间用于多次迭代。经过Log10转换的数据在拟合期间稳定方差。使用bootstrap方法构造参数值的置信区间。对线性化数据进行Pearson相关、异方差和自相关检验(分别为Breusch-Godfrey和Durbin-Watson检验)。拟合程度通过均方根(RMS)和平均*百分比误差(MAPE)进行评估。没有计算R平方统计量,因为它不适用于非线性系统。修正的Akaike信息准则(AICc)用于在不同复杂度的竞争模型之间一定程度地执行模型选择。

结果

复现摩尔定律

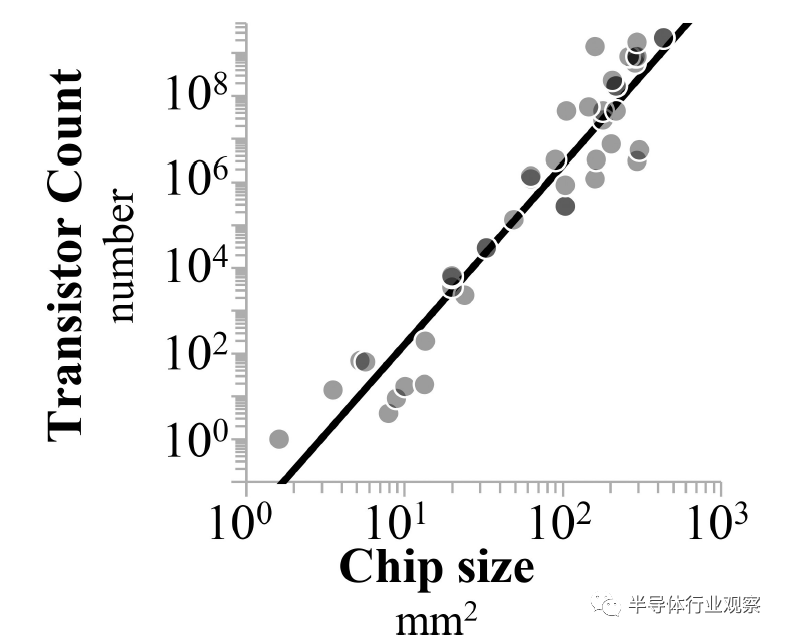

最初,摩尔定律是通过跟踪每个芯片上晶体管的数量(T)作为两个不同相位的时间函数来体现的。14个月和25个月的翻倍时间分别与摩尔1965年和1975年的估计相似。同时,处理器芯片面积(A)也呈现指数斜率,倍增时间为8.3年(r=0.94,P<0.001)。回归这两个变量表明芯片尺寸通过幂律关系与晶体管数量耦合(图2)。这证明了“每个芯片的晶体管数量”可能是电路密度的一个有偏差的描述。晶体管计数的增加并不明确表明晶体管的小型化,因为增加处理器上的晶体管数量也可以通过增加芯片尺寸来实现。

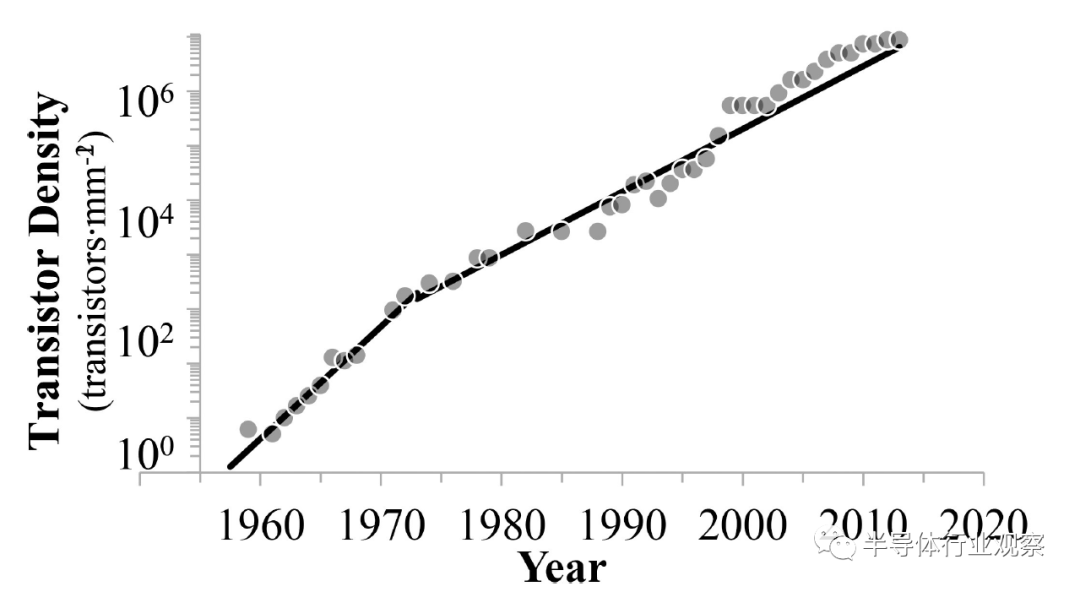

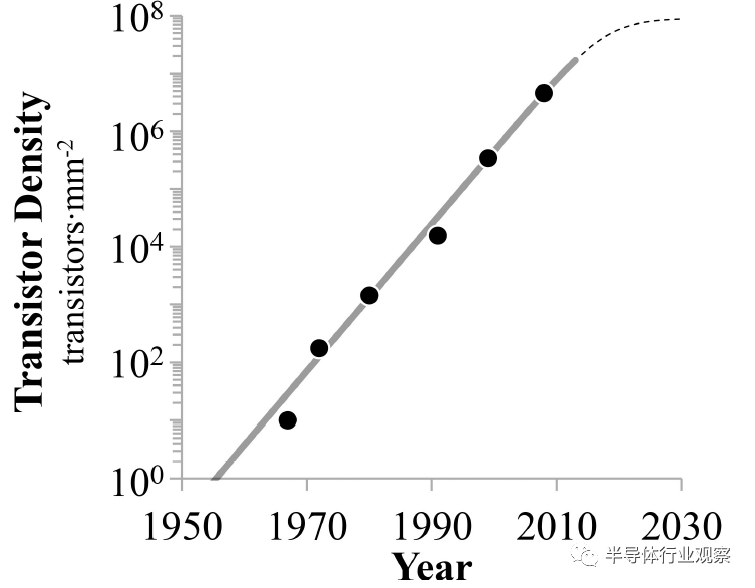

晶体管密度

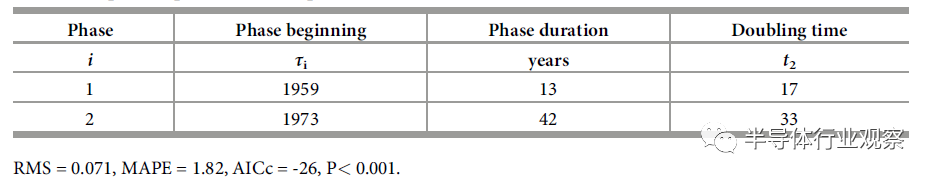

基于这一发现,我们将晶体管密度定义为每单位面积的晶体管数量。然后将这些重定标数据拟合到摩尔定律分段指数模型(方程式1),结果如图3所示。*阶段和第二阶段的倍增时间分别为17个月和33个月(表1)。这些数值比Moore报告的12到24个月的数值快近30%(见引言)。然而,数据表现出显著的异方差(P=0.024)和自相关(P<0.001)。事实上,这种数据高于或低于模型预测值的偏差,尤其是1999年以来的所有数据远高于预期值,意味着分段指数模型不适用于这些数据。

处理器进化的S形(Sigmoid型)趋势

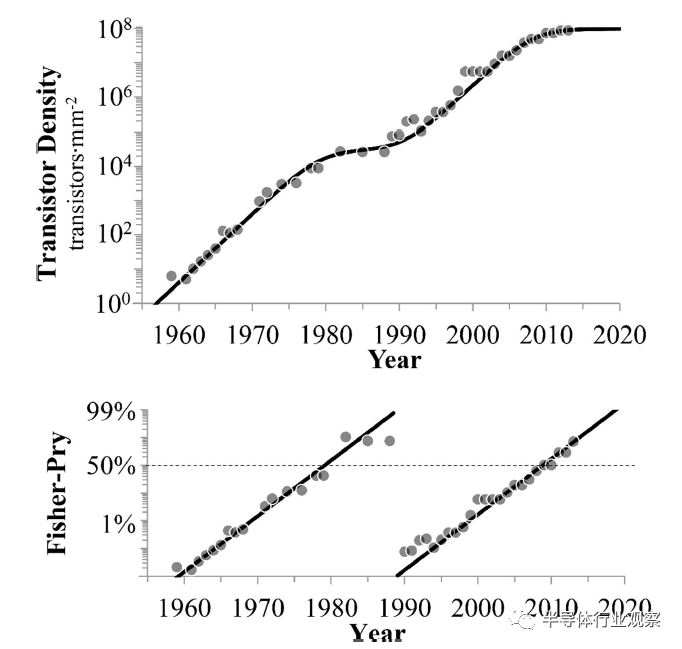

将晶体管密度拟合到等式(2),从而形成明确的双逻辑斯蒂(bi-logistic)趋势(图4A)。有趣的是,两个阶段的特征时间(Δti)均为9.5年。这些不同增长曲线的中点出现在1979年和2008年左右,其间相隔约30年。*个增长动力在对数累积分布饱和约一半时饱和(表2)。图4B显示了将线性化的双逻辑斯蒂分解为其组成阶段。双对数模型(AICc=-40)的模型选择标准值低于分段指数模型(AICc=-26)。

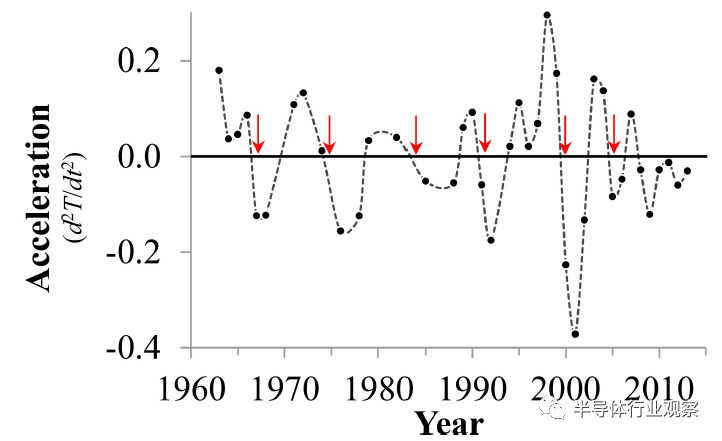

根据摩尔定律,数据应显示指数增长曲线的独特加速特性。然而,数据显示出明显减速的波动趋势,通过多个拐点,二阶导数从正到负交叉,达到多个极小值(图5)。当然,随之而来的是快速加速

图2.最新处理器尺寸与晶体管数量之间的幂律关系(T/A4.4,P<0.001)。

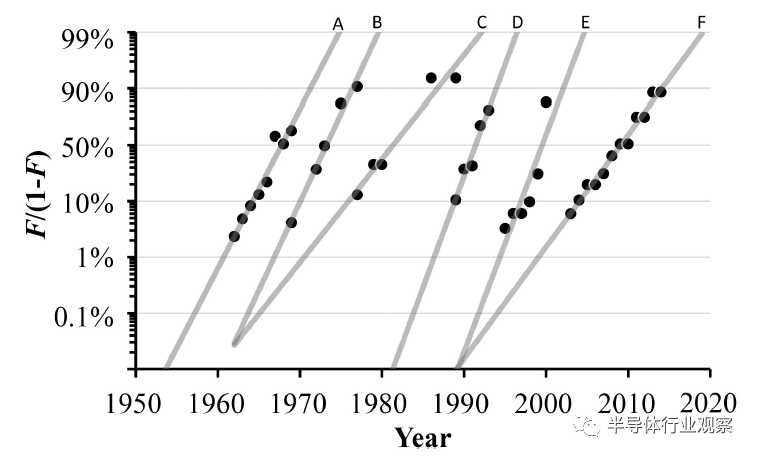

CPU晶体管密度数据中包含的这些多相动力学表明六个显著的增长期,即晶体管密度的增长率迅速增加,然后是至少连续三年的稳定期。图6显示了从上面导出的信息对单个逻辑小波的分解。表3总结了多逻辑模型参数值。这些生长阶段的持续时间为7至11年(平均=9年)。平均生长速率常数为0.8 yr-1,对应于6年的平均特征时间,晶体管密度的典型相位转换约为10倍。因此,多逻辑斯蒂趋势(multiple logistic trends)符合技术更替的顺序模式。

讨论

本文的研究试图检验计算机处理器技术中简单指数趋势的假设。图6中的趋势线A-B和D-E表示驱动*条逻辑曲线的技术饱和并被新技术取代的顺序模式。有趣的是,这两种趋势的发源相同,但本身却有差异(图6B、6C、6E和6F),可能表明性能方面的自蔓延增长。在每个阶段,晶体管密度在大约六年内至少增加了十倍,在之后的至少三年中,增长率可以忽略不计。晶体管的快速小型化仅在晶体管历史的三分之二时间内实现。

从经济角度来看,这是有其现实意义的,因为需要通过持续生产基于现有技术的产品以及引进新产品来增加收入。这使得每一次新的进步所需的研究和开发投资成倍增长,从而实现经济回报。小型化浪潮(密度更大,甚至物理上更小的芯片)可能会使市场成倍增加,就像以单位(如晶体管数量)衡量的不断增长的芯片尺寸一样。

这里描述的CPU的瞬时逻辑斯蒂趋势指向了推动流程的技术进步。1959年在仙童半导体公司开发的*个商用平面晶体管正是基于硅晶体管的证实和光刻技术的使用,这两种技术分别于1954年和1955年开发于贝尔实验室,作为*阶段(A线)的基础。金属氧化物半导体场效应晶体管(MOSFET)是未来所有晶体管技术的基础1964年由General Microelectronics将其专利化并商业化,这可能是第二逻辑小波(线B)的开始。硅栅技术(SGT)最早由英特尔实现,是所有后续微处理器的先驱,从1971年发布的4004和8080便是第三波(C线)趋势的开始。1977年获得专利的高密度短沟道MOS(HMO)大幅提高了1978年发布的8086的晶体管密度。

1989年推出的80486允许在芯片上集成更多的晶体管,从而使集成复杂电路成为可能,如8KB缓存和浮点数学协处理器(E线)。1982年被证实可行的深紫外准分子激光光刻技术在20世纪90年代得到了商业应用,这可能是第六个小波(F线),因为自1998年以来发布的所有处理器都是基于该技术制造的。第三波和第六波背后的技术可能是晶体管发展过程中最重要的技术,这两种技术对该行业的发展都有二十年的影响。本文简要介绍了一些关键的因果关系发展,更详细的介绍我推荐读者阅读Seitz、Einspruch和Lojek的著作,以及IEEE文章“25 Microchips That Shook the World ”和Computer History Museum on The Silicon Engine网站上的文章“A Timeline of Semiconductors in Computers”。

图3.每年*进的集成电路密度(每平方毫米晶体管数量)。这两个指数增长阶段的特点是分别增长17个月和33个月。数据是异方差和自相关的,自1999年以来一直低估所有数据。

表1.分段指数模型参数值。

图4.晶体管密度的时间趋势。A) 数据呈双逻辑曲线。B) 单个趋势的分解和线性化表示为两个阶段中每个阶段的增长百分比。参数值如表2所示。

表2.双逻辑参数值。

图5.近似二阶导数显示数据中复杂的加速和减速模式。箭头表示增长率下降的拐点。

图6.将数据分解和线性化为相应的单个对数趋势,突出显示晶体管演化的不同阶段。拟合模型参数值见表3。

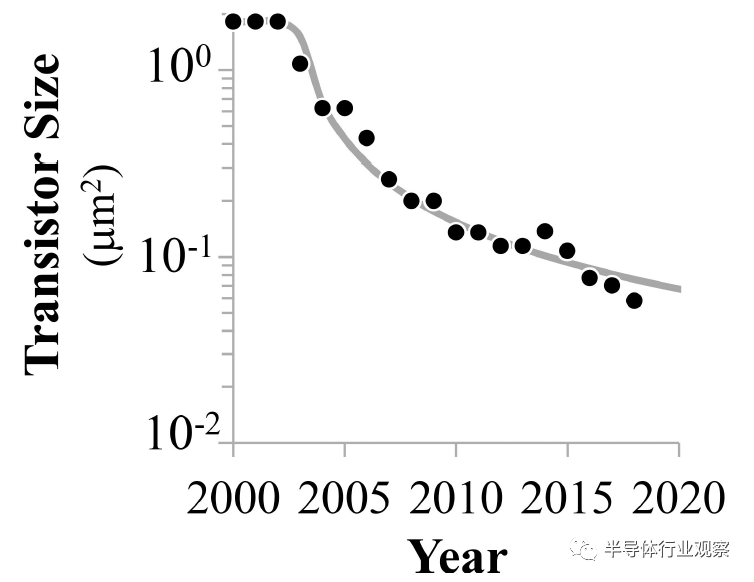

本文介绍的方法的另一个优点是能够跟踪平均晶体管尺寸的变化,这是密度函数的倒数,这与由“最小特征尺寸”定义的传统技术节点不同。自2000年以来的数据显示小型化趋势显著减慢(图7),而即使是相对重要的进步也只能使晶体管小型化保持在这种减速趋势上,如英特尔的3D三栅极技术。

在过去二十年中,晶体管小型化的进展大幅放缓,如果假设这一趋势继续下去,这似乎意味着偏离了半导体的国际技术路线图。这也可以解释目前在获得10nm、7nm或更小工艺的制造技术方面存在的困难。由于每个技术节点的“亚波长间隙”,芯片制造面临的挑战有所增加。事实上,过去十年已经表明,应变SiGe、高k金属栅晶体管、解析度增强技术和FinFET电路允许晶体管密度持续增加,尽管如此,从图中还是可以看到线性扩展速度明显较慢。

已知的物理定律对集成电路施加的基本限制已被计算出来——超出当前制造能力的许多数量级。有人认为,随着每个芯片核数的增加,数据并行性能够使计算性能加倍。这似乎不太可能,因为只有一些任务才可以高效地进行多线程处理,并且改进的不是速度,而是指令的并发性。系统上的其他物理约束,如热限制,也是不容易的。这些因素,以及快速增长带来的经济限制可能至少与物理限制同等重要。尽管有重大的技术和科学进步,晶体管小型化的当前阶段正在经历小型化率的衰减,这是逻辑模型中点附近动力学的特征。

英特尔于2014年停止报告其产品的晶体管数量和芯片尺寸。在过去五年中,只有估算数据可用于此分析,但这些数据无法由作者确认。尽管如此,这些估计似乎验证了模型,并为这种方法的性能提供了证据,而处理器小型化趋势没有显著变化。即使据报道晶体管数量增加,处理器芯片的尺寸也在继续增加,显然抵消了晶体管密度缓慢提高的影响。

根据本文所展示的分析,晶体管小型化的下一个增长动力即将到来。什么样的挑战才能引发一个足够大的市场,以使克服障碍所付出的努力是值得的?极大可能是以模仿生物智能为目的人工智能(AI),包括从一系列经验中获取新知识以逐步解决更多任务的能力,以及提供同理心和想象力的能力。人工智能研究人员在算法上不断进步,越来越需要硬件来处理大量数据和训练人工智能模型。芯片设计者在越来越大的芯片中嵌入大量的快速内存,以处理需要大量通信但相对容易计算的人工智能训练算法。例如,Xilinx(目前)开发了世界上*的现场可编程门阵列,拥有900万个系统逻辑单元和350亿个晶体管,这是迄今为止单台设备上最高的逻辑密度,旨在进一步提升机器学习、视频处理和传感器融合的复杂算法的开发。

创业公司Cerbiras吹捧有史以来*的芯片——晶圆级引擎(WSE),其尺寸是*图形处理单元(GPU)的56倍——GPU在人工智能和机器学习的计算平台上占据主导地位。晶圆级芯片有1.2万亿个晶体管,嵌入了400000个AI优化内核(比*的GPU高78倍),芯片内存增加了3000倍。

“5G”基础设施承诺多Gbps峰值数据速度、超低延迟、更高的可靠性、巨大的网络容量、更高的可用性,并为更多用户提供更统一的用户体验。所需的基础设施,包括移动设备、汽车、无人机和物联网等接入点,将构成大量硬件。例如,每辆车至少需要10个摄像头和32个传感器才能实现高水平的自主驾驶。考虑到数据的预期增长,5G网络将在本Zettabyte十年结束时达到容量,而在2030年左右,我们将进入全球总体数据生成的Yottabyte时代。简言之,人工智能的世界需要巨大的处理能力来解决复杂问题,即使使用相对简单的算法,也需要为机器学习进行芯片级优化。

一些研究人员预测,硅基摩尔定律将在2020年左右失效。我们的分析表明,这种可能性可能被低估了。过去十年晶体管密度的演变符合线性趋势,意味着缓慢和渐进的进步,但也意味着与摩尔指数定律的实质性背离。在这里,我们通过从六个已标出的logistic小波的拐点进行一次超logistic跳跃(图8)。实际上,我们将图6中的六个增长动力集中在一个点上。结果是一个预测——晶体管密度演变可能确实饱和,但在一个或两个以上的增长出现之后。

(In effect, we have concentrated each of the six growth pulses in Fig 6 into a single point. The result is a projection that transistor density evolution may indeed saturate, but after one or possibly two more pulses.)

对晶体管小型化的减速和平台期的观察表明了固有的技术困难以及可能的策略。晶体管的数量多越来越不一定是*解,因为在能源效率或冷却方面的限制要求集成电路的某些部分在运行期间断电,这种设计挑战被称为“暗硅”。计算机行业如何继续发展和创新?

如上所述,为多核处理器允许的并行计算而优化的软件的进步是*化处理能力的重要途径。实现浸没式光刻和EUV(immersive excimer laser and EUV metrology)的工作已经进行了十多年。目前正在对纳米晶体管和单原子晶体管进行新的研究,同时另一种可能是量子计算。2019年,Alphabet声称量子计算取得了突破,一个名为“Sycamore”的可编程超级计算处理器使用可编程超导量子位在52个量子位上创建量子态,对应于253维(约1016维)(dimension 253 (approximately 1016).)的计算态空间。公布的基准测试示例报告说,在大约200秒的时间内,Sycamore完成了目前*进的超级计算机需要大约10000年的时间来完成的任务。这些技术中的每一项都优势,同时也有实现新的快速增长阶段所必须克服的障碍。未来的挑战不仅仅是驱动整个行业的根本经济因素。

表3.双逻辑参数值。

图7.自2000年以来平均晶体管尺寸的减小。

图8.一个“hyperlogistic”函数拟合到六个确定的logistic小波的拐点。

这项工作报告了基于信息论的广义逻辑模型的统计偏好,并试图通过晶体管密度的维度来描述计算机处理器演化的复杂系统,这突出了晶体管的小型化。集成电路复杂性的标准度量可能不适合于理解处理器的发展,因为芯片上晶体管的数量与芯片的大小有关。此外,时间序列数据建模的统计特性在文献中通常被忽略。例如,摩尔定律逐步指数模型存在自相关,由于数据的异方差性,低估了33%的数据。不幸的是,许多其他研究都没有数据对经验数据中是否存在不连续性进行独立测试。

总之,我们展示了晶体管密度动力学的特征是一系列的加速和减速,这为摩尔定律提供了另一种观点。尽管模型复杂度增加,但双逻辑模型在统计上优于摩尔定律。基于信息的统计检验证实该模型比摩尔定律更为节约(parsimounious)。此外,尽管复杂度要高得多,但多元逻辑的性能甚至更好,其数量级较低的方差抵消了过度拟合的风险。此外,直接从数据估计特征时间和中点的参数值可以*限度地减少过拟合问题。这些发现对晶体管演化的指数过程的假设提出了质疑,并表明更复杂的动力学正在发挥作用。

分析人士试图将摩尔定律应用于其他技术领域,包括DNA测序和光伏等。我们对微处理器发展的回顾强调了选择正确Y轴的重要性。通过小型化和芯片密度,可以像通过芯片计数一样深入理解计算的发展。