光刻工艺是半导体器件制造工艺中的一个重要步骤,该步骤利用曝光和显影在光刻胶层上刻画几何图形结构,然后通过刻蚀工艺将光掩模上的图形转移到所在衬底上。

自1961年*台光刻机诞生以来,光刻机经历了接触式→接近式→投影式的发展路线,如今以投影式中的步进扫描式光刻机为主流。

在不同的阶段,每一代光刻机都遇到了前所未有的挑战与难题,与此同时,光刻技术也在这个过程中不断演进。

1、光刻技术的发展路径,接触式光刻技术

接触式光刻技术出现于20世纪60年代,是小规模集成电路时期最主要的光刻技术,有着良率低、成本高的特点。

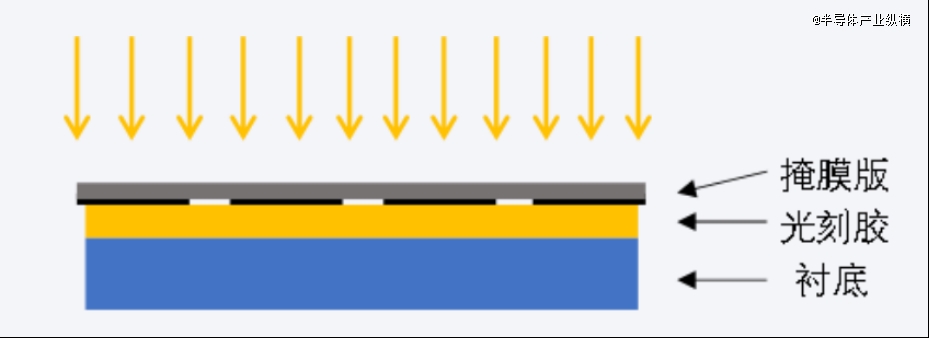

接触式光刻示意图

接触式光刻技术中掩膜版与晶圆表面的光刻胶直接接触,一次曝光整个衬底,掩膜版图形与晶圆图形的尺寸关系是1:1,分辨率可达亚微米级。接触式可以减小光的衍射效应,但在接触过程中晶圆与掩膜版之间的摩擦容易形成划痕,产生颗粒沾污,降低了晶圆良率及掩膜版的使用寿命,需要经常更换掩膜版,故接近式光刻技术得以引入。

接近式光刻技术

接近式光刻技术广泛应用于20世纪70年代,接近式光刻技术中的掩膜版与晶圆表明光刻胶并未直接接触,留有被氮气填充的间隙。

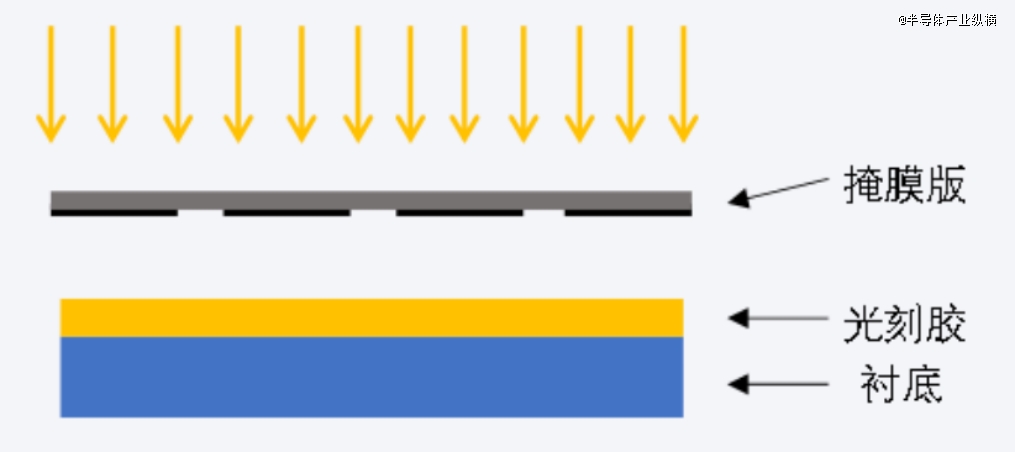

接近式光刻示意图

接近式光刻技术的特点是最小分辨尺寸与间隙成正比,间隙越小,分辨率越高。缺点是掩膜版和晶圆之间的间距会导致光产生衍射效应,因此接近式光刻机的空间分辨率极限约为2u m。随着特征尺寸缩小,出现了投影光刻技术。

投影式光刻技术

20世纪70年代中后期出现投影光刻技术,可以有效提高分辨率。

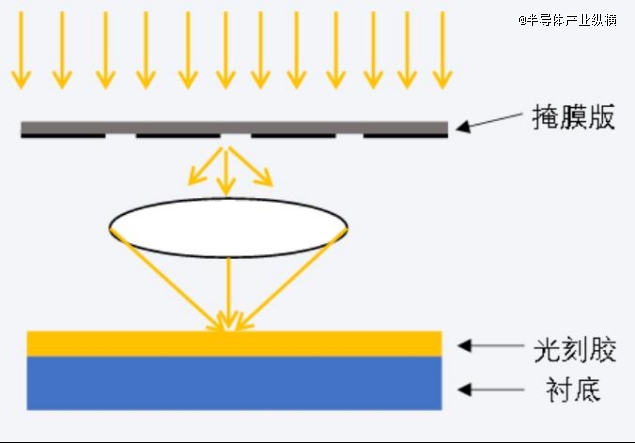

投影式光刻示意图

基于远场傅里叶光学成像原理,在掩膜版和光刻胶之间采用了具有缩小倍率的投影成像物镜。早期掩膜版与衬底图形尺寸比为1:1,随着集成电路尺寸的不断缩小,出现了缩小倍率的步进重复光刻技术。

步进重复光刻技术

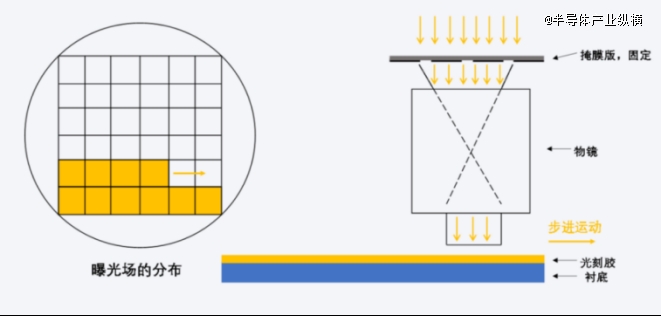

步进重复光刻示意图

步进重复光刻主要应用于0.25微米以上工艺,光刻时掩膜版固定不动,晶圆步进运动,完成全部曝光工作。随着集成电路的集成度不断提高,芯片面积变大,要求一次曝光的面积增大,促使更为先进的步进扫描光刻机问世。

步进扫描式光刻机

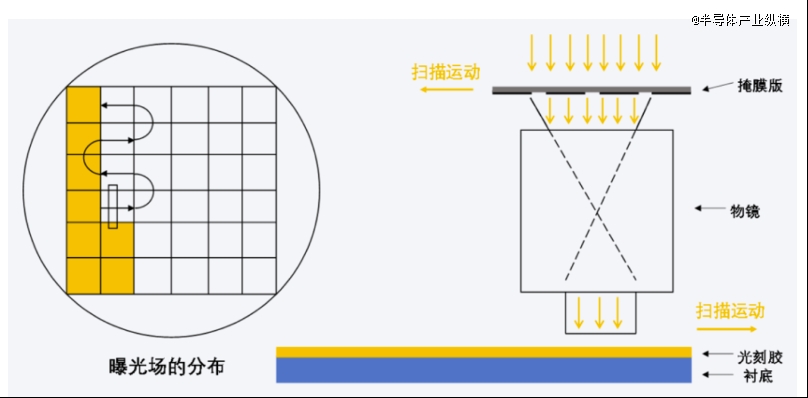

步进扫描光刻示意图

当制程工艺发展到0.25微米后,步进扫描式光刻机的扫描曝光视场尺寸与曝光均匀性更具优势,逐步成为主流光刻设备(DUV和EUV)。其利用 26mm x 8mm 的狭缝,采用动态扫描的方式(掩模版与晶圆片同步运动),可以实现 26mm x 33mm 的曝光场。当前曝光场扫描完毕后,转移至下一曝光场,直至整个晶圆曝光完毕。

自1990年SVGL公司推出Micrascan I步进扫描光刻机以来,光刻机产业就进入了DUV时代,通过多重曝光等技术手段,一直到7nm芯片量产,DUV都是市场的统治者。

然而随着制程演进到5nm,DUV和多重曝光技术的组合也难以满足量产需求了,EUV光刻机就成为前道工序的必需品。之后制程节点不断演进,行业对EUV光刻机的要求越来越高,对其发展前景和发展路径也提出了更多期待。

对于未来光刻技术的发展,业界正积极寻找高精度且经济的方法,以在晶圆上生成图案。多家公司/研究机构已公布了其研究进展,一起来看看他们为光刻技术带来了哪些新的选择。

2、选择之一:High NA EUV光刻机

光刻机所使用的光源波长从最早的紫外光源(ultraviolet, UV),如g线(波长436 nm)、i线(波长365 nm)光源,发展到以KrF(波长248 nm)、ArF(波长193 nm)为代表的深紫外光源(deep ultraviolet, DUV),再到现在波长13.5 nm的极紫外光源(extreme ultraviolet, EUV)。

随着光源波长的不断缩短,光刻机单次曝光分辨率不断提升,目前*进的EUV光刻机曝光分辨率为13纳米,可用于3 nm制程芯片的生产。

如今,台积电、三星、英特尔等芯片制造公司之间的竞争已进入先进制程赛道。在此过程中,EUV极紫外光刻设备也已经成为各厂商争夺的焦点。

据悉,2024-2025年,台积电将接受60台EUV光刻机,预估总费用将超122亿美元;英特尔率先拥抱全球*台High NA EUV光刻机;三星也在向High NA EUV光刻机跃跃欲试,试图追赶台积电。

然而追逐*进的光刻机的同时,是喜悦的也是痛苦的。

喜悦在于,*得到*进的光刻机意味着可以极大地提升其芯片制造能力和效率,帮助公司在未来先进制程技术的竞争中取得先行优势。

痛苦在于,EUV高昂的售价令各大芯片厂商苦不堪言。据悉,目前0.33NA EUV光刻机的售价约为1.81亿美元每台,新一代的High-NA(0.55NA)EUV倍增至2.9-3.62亿美元一台。而进入1纳米以下的埃米世代后,ASML将计划推出更先进Hyper-NA(0.75NA)EUV光刻机设备,其售价则有可能超过7.24亿美元。

这一方法显然足够精细但不够经济。因此业内也有不少机构正在探究High NA EUV的降本之法,他们将主要精力放在了提升光源分辨率上。

ASML当前所采用的激光等离子体EUV光源(EUV-LPP)价格昂贵,效率低下,光电转化率仅为3%-5%。要提升功率,有几条发展路径可供选择:有人利用传统的LPP光源系统,在已有基础上,不断增加功率;还有人采用分时高功率光纤激光器射击液态锡靶技术,用这种方法制造的光源,其光源功率有望超过传统LPP数倍。

使用能量回收型直线加速器(ERL)的FEL(自由电子激光)方案也是一种办法。日本高能加速器研究组织(KEK)的研究人员认为,如果利用粒子加速器的力量,EUV光源的获取可能会更便宜、更快、更高效。

FEL利用电子在磁场中的运动产生*激光,其效率比普通EUV光源高出一倍,能量转化率超过30%,且拥有成本低、功率大等优势。在电力消耗方面,FEL光源也要远低于EUV-LPP光源。此外,EUV-FEL还可升级为BEUV-FEL,以使用更短的波长(6.6-6.7 nm)实现更精细的图案化。它还可以可变地控制FEL光的偏振,以实现High NA光刻。

据悉,目前业界已经设计了一种基于能量回收直线加速器(ERL)的FEL光源用于未来的光刻,并且已经研究和开发了主要组件。FEL光源在EUV功率、升级到BEUV-FEL、High NA光刻的偏振控制、电力消耗和每台光刻机的成本方面具有许多优势。

EUV-FEL光源也被认为是未来光刻最有前途的光源。

不过,对于光刻技术的未来发展,业内还有不少人持有不同看法。

3、选择之二:纳米压印技术(NIL)

纳米压印和光刻技术的“较量”由来已久。

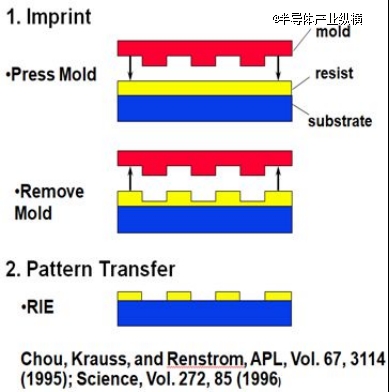

纳米压印是基于高分子模压技术的微纳加工技术。纳米压印需要一个模板,就像活字印刷的模板上刻着要印的字,纳米压印的模板上是需要制造的纳米结构,然后通过加热加压,把模板上的纳米结构复制到纳米压印的材料里。

形象一点可以将其类比为活字印刷术。

与光刻技术相比,纳米压印技术具有以下优势:

成本更低:相比光刻技术,纳米压印技术的成本更低,主要原因是纳米压印设备相对便宜且工序简单,更易于批量操作。

精度更高:通过精心设计和制造高精度的“印章”,纳米压印技术可以实现优于10nm的高精度电路图印制,为芯片制造提供更高的精度保障。

更广泛的应用领域:纳米压印技术不仅适用于逻辑芯片和存储芯片的制造,还可以广泛应用于DOE、AR/VR衍射光波导、生物芯片、LED等领域的量产,具有较大的市场潜力。

目前纳米压印在LED、AR、VR等领域被广泛运用。纳米压印已发展二十余年,但在相当长一段时间里,由于纳米压印的制成品缺陷多、良率低,不太被半导体领域接受,光刻技术则发展得更快、更好。

而在近十年,随着纳米压印对工艺的优化和控制精度上了一个台阶,一度被光刻否定的纳米压印,迎来了高光时刻。

不过纳米压印技术也有它的短板,它是一种物理接触式的加工技术。在物理接触的过程中,容易产生一些外部缺陷。而半导体行业对缺陷的容忍度非常低。业界有一部分人认为纳米压印是非常有前景的技术,还有一部分人认为它的缺陷率比较高,不适合半导体加工。

佳能公司在传统的光刻领域落后于ASML公司之后,一直在半导体制造方向寻找新的突破点,它的探究重点之一就是纳米压印技术。

去年10月中旬,佳能宣布推出FPA-1200NZ2C纳米压印半导体制造设备,可制造5nm芯片。据佳能公司CEO透露,设备售价将“比ASML的EUV光刻机少一位数”。

璞璘科技创始人葛海雄去年年底曾表示:从最近的报道来看,佳能公司的纳米压印各项技术指标已经与DUV的光刻技术持平,有一些指标甚至达到了EUV的光刻技术。

关于纳米压印技术的未来,葛海雄表示,依据佳能提供的技术参数、指标,纳米压印有可能为半导体领域创造一些有益的补充,因为ASML、尼康的半导体光刻设备已经在产线上被广泛采用了,纳米压印可以看成是光刻技术的衍生。

因此,纳米压印技术也被称为未来半导体制造的核心技术。

目前,不少科研机构和厂商都加大了纳米压印上的投入。除了佳能,国外厂商如EV Group、Nanonex Corp、Obducat AB、SUSS MicroTec等公司已出产纳米压印光刻设备。国内也有不少厂商在纳米压印赛道上加紧布局,如青岛天仁微纳、苏州苏大维格、歌尔股份、苏州光舵微纳、昇印光电、新维度微纳、埃眸科技等。

获得华为哈勃青睐的国内头部厂商天仁微纳目前产品涵盖整机设备、模具、压印材料,研发了多款高精度紫外纳米压印设备,已经实现*150/300mm基底面积上高精度(优于10nm )、高深宽比(优于10比1)纳米结构复制量产。

对于纳米压印技术*落地的领域,或许是存储芯片。

在芯片制造领域,目前最契合纳米压印技术的,就是存储芯片,尤其是3D NAND、DRAM等存储芯片。从佳能规划的纳米压印设备路线图来看,纳米压印应用将从3D NAND存储芯片开始,逐渐过渡到DRAM,最终实现CPU等逻辑芯片的制造。

存储厂商在芯片制造上对成本把控极为严苛,同时设计的余量可以承受一定的缺陷而不影响成品率,放宽对缺陷的要求,所以目前已经有不少存储厂商计划使用纳米压印技术来制造存储芯片。

铠侠、东芝等日系存储厂商很早便开始布局纳米压印技术。今年3月,美光公司宣布计划率先支持佳能的纳米印刷技术,从而进一步降低生产DRAM存储芯片的单层成本。此前,内存大厂SK海力士也引入了佳能纳米压印机,用于进行3D NAND的生产测试。

纳米压印技术与存储芯片相结合,将大大提高存储厂商的生产效率,并降低成本。纳米压印设备在芯片制造领域大规模商用化后,其优势将更加明显。

因此纳米压印技术也被称为最有机会代替现有光刻技术的技术手段。

4、选择之三:电子束光刻(EBL&MEBL)技术

说到电子束光刻技术,在这里要再提及一下光刻技术的原理。

众所周知,光刻是整个微加工工艺中技术难度*,也是最为关键的技术步骤。所谓光刻就是通过对光束进行控制,在一层薄薄的光刻胶表面“刻蚀”出我们需要的图案,光束照过的位置光刻胶的化学性质会发生变化,通过显影液的浸泡会使照射过的部分去除(正胶)或者保留(负胶)。

光源的波长是影响光刻精度的主要原因,由于光源波长的限制,X射线曝光可达到50nm左右的精度,深紫外光源的曝光精度在100nm左右,而电子的波长较小,因而电子束光刻的加工精度可以达到10nm以内。

电子束光刻以其分辨率高、性能稳定,成本相对较低的特点,因而成为人们最为关注的下一代光刻技术之一。

电子束光刻按照曝光方式划分可分为两种,投影式曝光与直写式曝光。投影式曝光通过控制电子束照射掩模图形,将掩模图形投影至光刻胶表面,把掩模板上的图案转移到光刻胶上,原理类似于照相机,拍摄对象好比掩模板,光刻胶就像是胶卷,通过光线的照射把拍摄对象投影到胶卷上。

直写式光刻不需要掩模版,通过磁场直接控制电子束斑按照预设的轨迹在光刻胶表面照射,完成图案转移,就像是画画,铅笔类似于电子束,纸类似于光刻胶,而我们的手类似于磁场,通过手控制铅笔的移动完成图画的绘制。

由于基于掩膜的传统光刻技术,其成本正呈指数级攀升。无掩膜的电子束光刻技术则提供了补充性选项,因为不需要昂贵的光掩模,直写技术很有吸引力。但单光束电子束光刻的吞吐量太慢,对于批量 IC 生产来说成本太高。分析人士也直言,直写真正的问题是吞吐量。直接写入光刻技术,即使有数十万甚至一百万个光束,但对于晶圆光刻来说也太慢了。

因此,单光束直写工具只能用于复合半导体和光子学等小众应用。

为了解决写入慢的难题,Multibeam给出了它的答案。

近日,电子束光刻技术的主要参与者Multibeam推出了 MB Platform,——全球首创的多柱电子束光刻 (MEBL:Multicolumn E-Beam Lithography )。据介绍,其新光刻系统是专为大规模生产而打造的系统。全自动精密图案化技术将用于快速成型、先进封装、高混合生产、芯片 ID、复合半导体和其他应用。Multibeam表示,公司刚发布的平台将以新的生产力优势彻底改变了电子束光刻,同时实现了高分辨率、精细特征、宽视野和大景深。

Multibeam 首席执行官兼董事长 David K. Lam 在接受采访时表示,Multibeam 可以使芯片制造的某些部分的生产效率比现有系统高出 100 倍。

在Multibeam 看来,这是一款改变了游戏规则的设备。不过,早在80年代,当时人们普遍认为光学曝光已经走到了尽头,电子束光刻是最有前景的替代手段,然而,30多年过去了,电子束光刻依然无法替代光学曝光。在两种光刻技术的发展方面逐渐形成了相互补充的格局。

随着科技的日新月异,新型光刻技术的涌现无疑为行业注入了新的活力。未来,这些创新的光刻技术将给半导体行业带来哪些惊喜,我们拭目以待!