当晶圆代工还在推进3nm时,2nm已经横空出世。一个曾经遥远的目标,随着摩尔定律的发展正在被台积电、英特尔、三星等巨头竞相追逐。

从各大巨头公布的进展来看,2025年将是2nm的决战之年。

01、2nm的追逐之战

在2nm的征战中,台积电、英特尔、三星从未缺席。

台积电一直走在先进制程的前列。根据台积电2021年的财报显示,5nm晶圆出货量占据了总营收的20%,7nm工艺技术占30%,也就是说先进制程芯片代工贡献了一半营收。

因此,台积电对于先进制程的重视不言而喻。台积电官方曾表示,其到2025年预计投入440亿美元用于研发,八成费用将用于先进制程。

在先进制程的路线图中,台积电*代3nm(N3)将于今年下半年量产,2nm将于2025年量产。在场地方面,台积电已经宣布将花费1万亿新台币(约2290亿元人民币)在台中扩大2nm产能布局。目前台积电的*2nm(新竹N2厂)正在申请土地使用权,计划于今年三季度动工。

英特尔同样进行了巨额的投入,在俄亥俄州宣布要投入200亿美元兴建晶圆厂,以及在欧洲投入360亿美元设厂。

英特尔已承诺到2025年重新获得芯片制造技术的*地位。在2021年年中首次披露了其1.8nm技术——它称之为18A技术。今年,英特尔首席执行官Pat Gelsinger表示,这项技术“比计划提前了六个月”,并将时间表提前到了2024年底。

面对先进制程的研发,三星在投资方面也毫不手软,宣布在未来三年内投资创纪录的2050亿美元,以保证在芯片制造领域的*地位。

三星电子今天宣布,已开始初步生产采用全环栅极 (GAA) 晶体管架构的3nm工艺节点。另外,三星也将2nmGAA工艺的量产时间定在2025年。

但是,良率问题已经成为围绕三星的阴影。在全球5/7nm工艺的主要客户中,只有高通、英伟达和IBM表示愿意采用三星电子的先进工艺技术,苹果、联发科、AMD、英特尔、博通都与台积电保持稳定的合作关系。在3nm的研发中,三星也多次因为良率过低推迟宣布正式的大规模生产。

02、2nm的全球渴望

面对2nm的诱惑,全球各地都在发力。

在美国方面,IBM在5月7日宣布了关于2nm的进展,声称其已打造出全球*2nm芯片制造技术。但是IBM公布的只是实验性质的预研项目,距离量产还有很远的距离。

日本则传出消息,想和美国合作研发2nm工艺制程,计划最早2025年在日本启动2nm制程国内制造基地。

欧盟同样想参与2nm的赛道。去年12月,19个欧盟成员国签署了一项联合声明,以“加强欧洲开发下一代处理器和半导体的能力”进行合作。其中包括为各行各业的特定应用提供*性能的芯片和嵌入式系统,以及向处理器技术的2nm节点发展的*制造技术。

欧盟希望在2030年,欧洲先进和可持续半导体的生产总值至少占全球生产总值的20%,较2020年提升一倍,制程瞄准2nm,能效达到今天的10倍。

03、GAA是2nm的最终选择?

关于2nm的结构选择一直是业内争议,每家公司都有不同的理念。GAA、Nanosheet和VTFET、CFET、2DTMD和CNT等新结构都曾出现在各大巨头的演讲稿中。

但面对2nm制程,台积电、三星、英特尔都不约而同的选择了GAA晶体管——纳米片FET(英特尔称其为RibbonFET)。

三星是全球*家使用GAA技术的公司,从5nm节点的finFET迁移到3nm节点的GAA。三星希望在GAA时代的竞争中获得一席之地。该公司宣布将在2022年推出3nmGAA的早期版本,而其“性能版本”将在2023年出货。

相比之下,英特尔和台积电计划在3nm扩展finFET,然后在2nm转移到GAA。台积电在3nm时保留了FinFET结构,从而降低风险。台积电的3nm是其5nm平台的全尺寸版本,但复杂度更高。

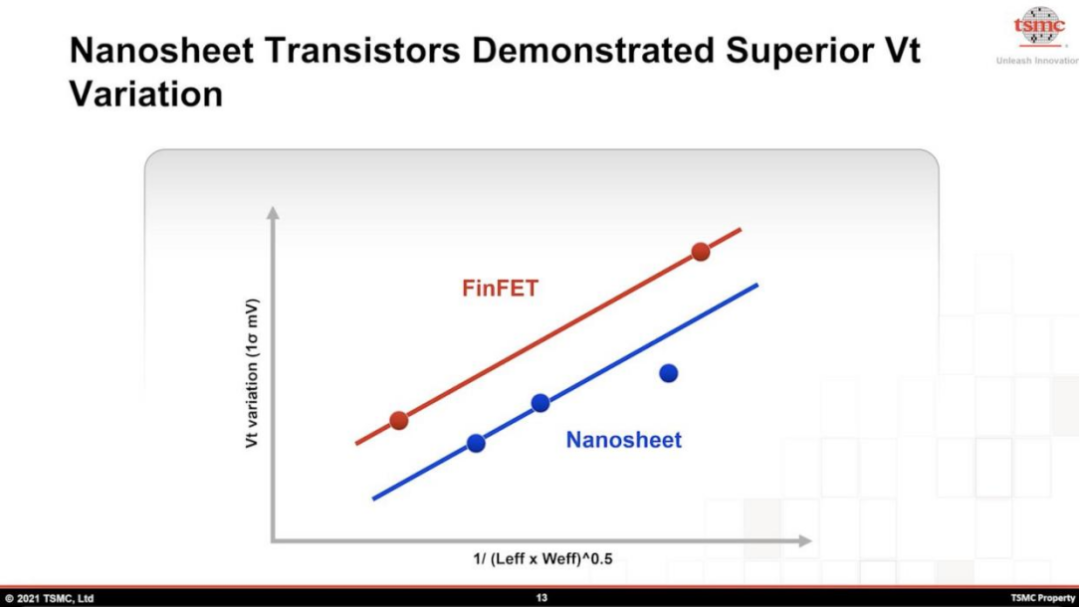

台积电的全环绕栅极式纳米片电晶体管(GAA nanosheet transistors),晶体管的通道在所有四个侧面都被栅极包围,从而减少了电能泄漏。这在当下晶体管体积越发接近原子体积时,将会越来越突出。

采用GAA架构,可以解决FinFET因制程微缩产生电流控制漏电的物理极限问题。与FinFET晶体管(下图红线)相比,Nanosheet(下图蓝线)能够实现更严格的阈值电压(Vt)控制。

来源:台积电

去年宣布研制出2nm芯片的IBM同样选择了纳米片工艺,在IBM的研究中纳米片也表现出更优秀的特性。

更高的计算性能和更低的功耗:由于GAA中更好的静电控制和更高的封装密度,纳米片提供了更好的功率性能设计点。与代工厂现有的最新*的7nm FinFET技术相比,纳米片技术在相同功率下提供超过25%的性能提升,或在相同性能下节省超过50%的功率。

更流线型设计的可变片宽:值得注意的是,纳米片技术是人工智能和5G时代计算机产品更好的架构材料,因为它通过极紫外光刻(EUV)实现了可变片宽。这使得器件设计更加通用,因为具有不同通道宽度的纳米片器件可以共同集成在同一芯片中,以进一步优化功率性能。

通道厚度控制:增加纳米片堆栈的通道层可以创建用于通道形成的原子级控制。FinFET不可能实现如此精确的沟道厚度控制,因为它是由光刻技术和RIE定义的,其中局部和全局工艺变化远高于外延厚度变化。

也正因如此,Nanosheet GAA或许会成为2nm的未来选择。

04、EUV光刻机的激烈竞争

工欲善其事,必先利其器。

在2nm的研发中,高NA的EUV光刻机是制造的关键设备。使用13.5nm波长EUV已被用于在7nm和5nm处对微小特征进行图案化。下一代版本High-NA EUV正在研发中,需要对3nm以上的更精细特征进行图案化。因此,下一代光刻机花落谁家也成为是否能量产2nm工艺的关键。

而按照ASML的数据,2021年一共出货48台EUV光刻机,其中,三星购得15台,台积电为20台,另外的13台则被英特尔、美光、SK海力士等厂商分走了。

而2022年,预计可以交付51台EUV光刻机,这51台就是三星、台积电、英特尔们争抢的重点。

英特尔早已抢下ASML下一代芯片制造系统TwinscanEXE:5200,其吞吐量超每小时220片晶圆(wph),预计将在2024年交付并投入使用。TwinscanEXE:5200相较于其他光刻机无论是生产能力(每小时生产超过200片晶圆)还是精度(0.55数值孔径)都有较大提高,这意味着谁拥有了便拥有了3nm,甚至是2nm时代的芯片霸权。

台积电研发高级副总裁米玉杰在上述研讨会上表示:“台积电将在2024年引入Hign-NA EUV光刻机,以开发客户所需的相关基础设施和图案化解决方案,并推动创新。”尽管之后其表示,台积电不会在2024年准备使用新的High-NA EUV工具进行生产,将主要用于与合作伙伴进行研究。

但Tech Insights芯片经济学家Dan Hutcheson说:"台积电在2024年拥有它,意味着他们可以更快地获得*进的技术。”

三星方面,三星集团副会长、三星集团实际控制人李在镕最近访问欧洲,拜访ASML。外界认为,李在镕此举最重要的目标是,向ASML买到自己需要的EUV光刻机,以保证晶圆代工业务的顺利进行。

05、3nm仍将是主流

在摩尔定律的继续推动下,工艺制程或许还会缩小。从IMEC展示的最新路线图中,最远能够看到2036年的0.2nm工艺。

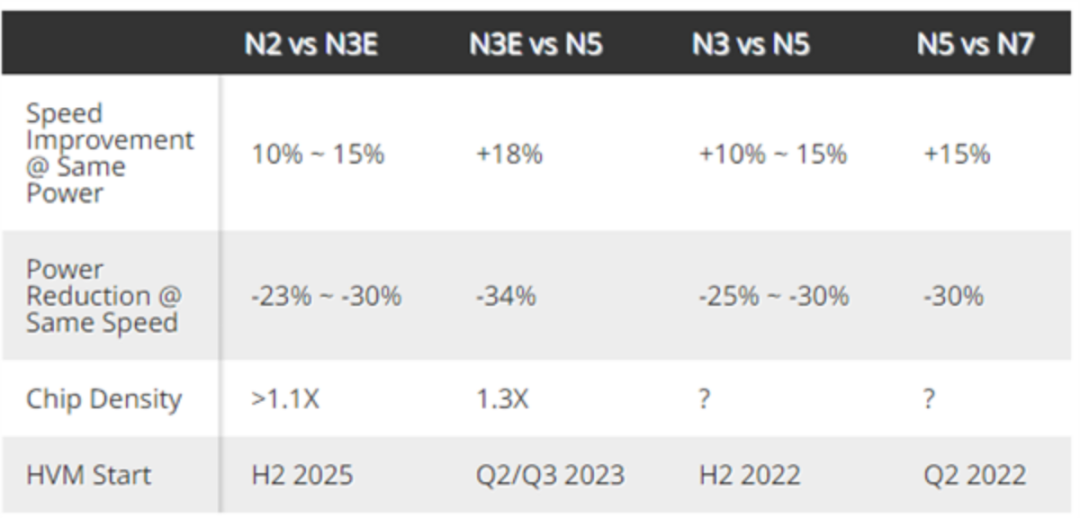

实际上,从目前台积电公布的性能提升来看,2nm之于3nm的提升,似乎不如3nm之于5nm。在同等能耗和复杂度下,N2的性能比N3高10%-15%。在相同速度和单位面积晶体管平均数目下,N2的能耗比N3低25%-30%,远远达不到摩尔定律密度翻倍的要求。

如果按照摩尔定律2年升级一代的水平发展的,未来芯片工艺还可以迭代下去。但就目前来说,3nm仍然将是长期的主流。

在2020年的ISSCC上,IMEC的Nadine Collaert女士提到,在3nm以下,很难再使得单个晶体管的性能再有提升,能做的只是提高集成度,降低功耗。所以从3到2,优化的程度可能并没有那么明显。

台积电也表示与N7和N5节点一样,N3将成为台积电另一个持久节点系列。尤其台积电2nm节点转向纳米片GAAFET技术,3nm节点系列将成为经典先进FinFET技术最后一个系列,许多客户预定还会采用几年或更久。台积电业务发展副总裁 Kevin Zhang表示:“我们确实相信3nm将是一个长节点。我们将继续看到该节点的大量需求。”

这也是为何台积电推出N3制程系列及FinFlex技术的原因。

实际上,我们没有必要过于神化先进工艺带来的变化,摩尔定律总有一天发展到尽头,但正如得胡正明先生说:“只要做出更加智慧的器件,半导体产业就会继续发展向前。”