摩尔定律作为半导体行业发展的经典规律,揭示了集成电路算力指数级增长对于整个产业链的颠覆性传导作用。但随着先进制成工艺所带来的巨大成本投入,维持摩尔定律的收益日渐收窄,厂商也开始刻意放缓技术迭代的速度。

本文从摩尔定律的内核实质出发,思考在“后摩尔时代”如何把握技术开发与产品应用之间的动态平衡。物联网、云、大数据、人工智能的发展为整个半导体产业链带来新的增量应用场景,但不同场景下的计算需求也对技术提出了更具象的要求。此外,中国芯片行业在这种背景下迎来了某种程度的利好。

源码资本经过分析研判*呈现第「22」期源码内参。

摩尔定律是一个半导体行业中的经验规律,而非客观物理世界中的规律。

维持摩尔定律,需要在资本研发投入和先进制程带来的收益之间寻找平衡。

增加AI计算能力、针对场景优化的一体化设计思路,推动计算芯片性能不断进步。

摩尔定律逐步失效,某种意义上,给了中国芯片产业追上来的机会。

摩尔定律的提出

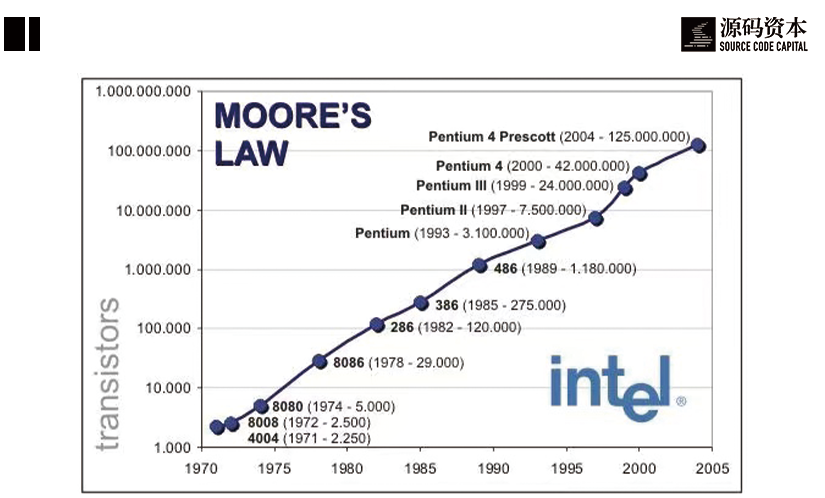

半导体行业有一条大家耳熟能详的定律——摩尔定律,它最早是由英特尔(lntel)名誉董事长戈登·摩尔( Gordon Moore)在1965年提出的。当时戈登·摩尔正在准备一个关于计算机存储器发展趋势的报告,在总结报告的绘制数据时,他发现了一个惊人的规律:每个新的芯片大体上包含其前任两倍的容量,每个芯片产生的时间都是在前一个芯片产生后的18~24个月内。

著名的“摩尔定律”由此诞生,它的准确表述是:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。直观来讲,就是每18个月,同样价钱可以买到的算力翻两番。

准确的说,摩尔定律是一个半导体行业中的经验规律,而并不是一个类似“牛顿三大定律”一样存在于客观物理世界中的规律。它所揭示的,是集成电路的算力呈指数级增长。

2005年前,Intel CPU处理器的发展速度,基本遵循摩尔定律:

图片来源:网络

先进制成的发展伴随着巨大的资本开支

摩尔定律逐步失效

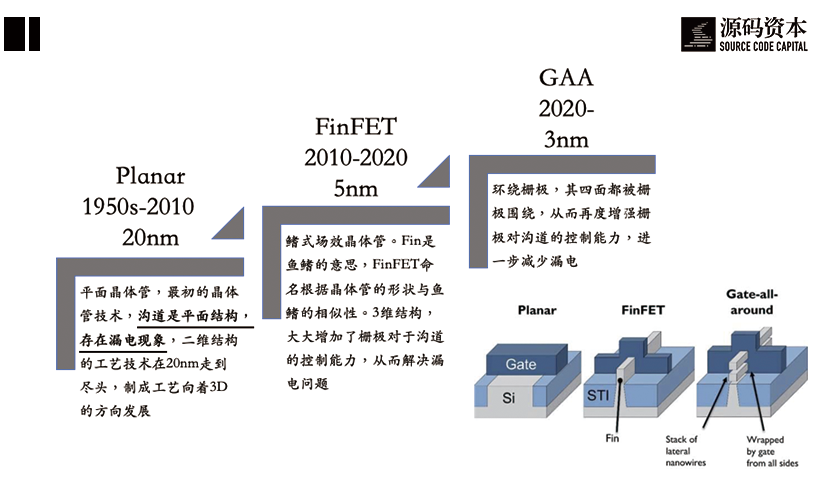

在半导体行业,制成工艺的不断迭代,是维持摩尔定律的重要底层驱动因素。现在半导体工艺上所说的多少nm工艺其实是指线宽,也就是芯片上的最基本功能单位门电路的宽度,因为实际上门电路之间连线的宽度同门电路的宽度相同,所以线宽可以描述制造工艺。目前先进制成已经发展到5nm。

先进的制成,带来两个好处:1)缩小线宽意味着晶体管可以做得更小、更密集,而且在相同的芯片复杂程度下可使用更小的晶圆,于是成本降低了;2)缩小线宽可以提升工作频率,缩减元件之间的间距之后,晶体管之间的电容也会降低,晶体管的开关频率也得以提升,从而整个芯片的工作频率就上去了。

先进制成的工艺不断进步:

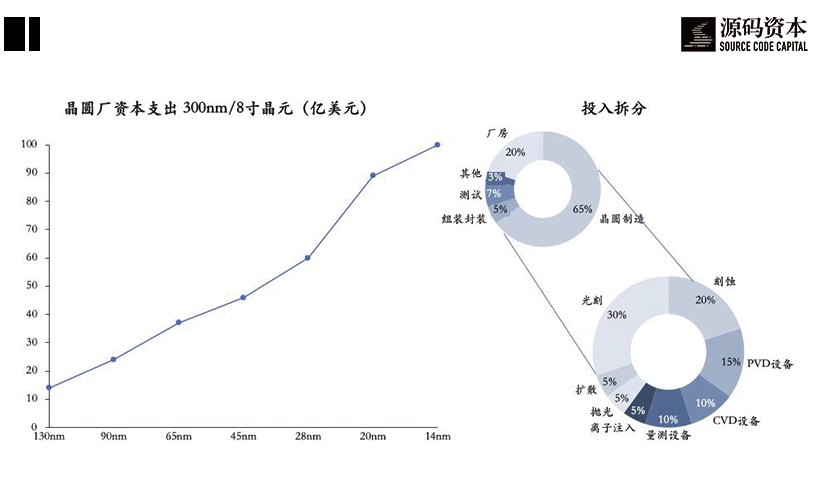

而先进制成的进步,背后是晶圆厂的不断投入,需要投入大量的资金建造厂房、购买*进的工艺设备。以量产14nm制成、300nm大小的晶圆厂为例,总体的投资在100亿美元左右,其中65%的资金需要投入到与晶圆制造相关的设备上,比如光刻机、刻蚀设备、物理气体沉积(PVD)设备、化学气体沉积(CVD)设备等与晶圆制造相关的设备。

建造晶圆厂的开支巨大:

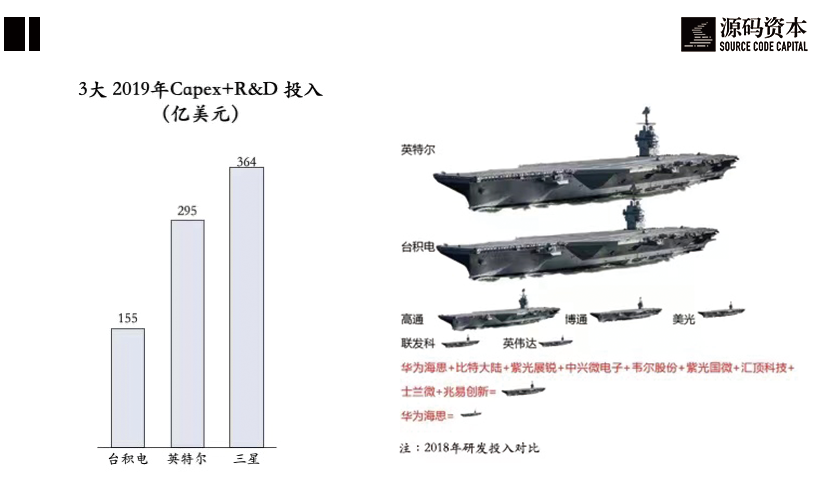

在全球范围内看,头部晶圆代工厂每年的资本和研发投入都超过百亿美元。台积电作为纯代工厂的头部厂商,2019年的资本和研发投入高达155亿美元。英特尔、三星作为IDM模式(集设计、制造、封装测试为一体的商业模式)的代表者,因有更为庞大的芯片设计团队,2019年的资本开支加研发投入分别达到了295亿美元和364亿美元。

头部晶圆厂的资本与研发投入,远大于纯设计类公司(Fabless模式):

图片来源:网络

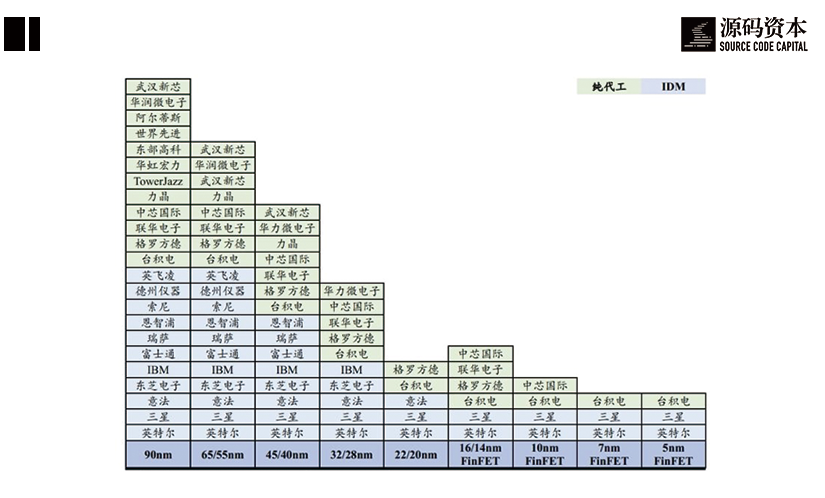

正是因为要想跟上摩尔定律的步伐,需要不断的资本开支投入,每一代制成的进步,都意味着有玩家掉队。目前,7nm及以下的制成工艺,仅台积电、英尔特、三星三家厂商可以掌握。中芯国际已经攻克了10nm的技术节点,正在进一步缩小与头部玩家的差距。

跟得上先进制成的玩家越来越少:

图片来源:网络

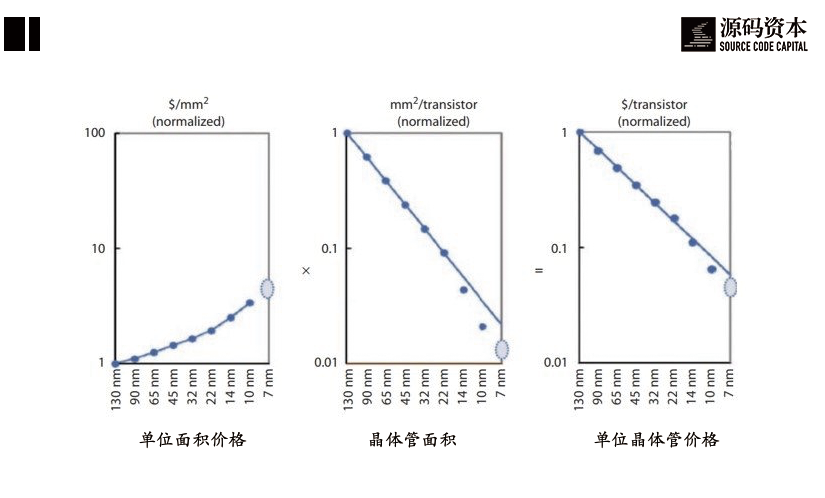

即使头部的3大玩家中,也只有台积电的先进制程是最成熟和稳定的。英特尔已经开始掉队, 从14nm到10nm的研发用了5年(2014-2019)。从14nm开始,英特尔单位面积的价格就已经开始呈指数级上升,为了控制单位晶体管的价格,英特尔激进的提升晶体管的密度,带来了严重的良率问题,目前10nm的先进制程仍存在良率爬坡与供给不足的问题,变相提升了产品的成本。

英特尔激进的提升晶体管密度:

图片来源:网络

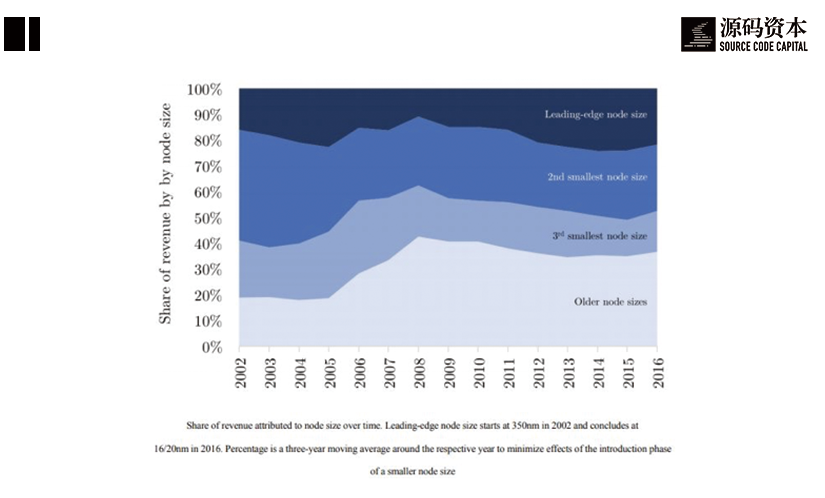

对于头部的晶圆厂来说,一方面,维持摩尔定律,就意味着每年超过百亿美元的资本投入和研发投入,是一项非常高的成本支出;另一方面,先进制成的大部分场景是在消费电子领域,如手机的高端旗舰机或者笔记本电脑,这部分市场加起来,仅占整个半导体市场的25%左右,随着全球智能手机和笔记本电脑的出货量已经到达高点并开始下滑,先进制成带来好处是在下降的。

先进制成的需求增长不足:

图片来源:网络

由此可见,维持摩尔定律的收益有限,头部的晶圆厂商也开始放缓先进制成迭代的速率,在资本研发投入和先进制程带来的收益之间,找一个平衡,摩尔定律失效了。

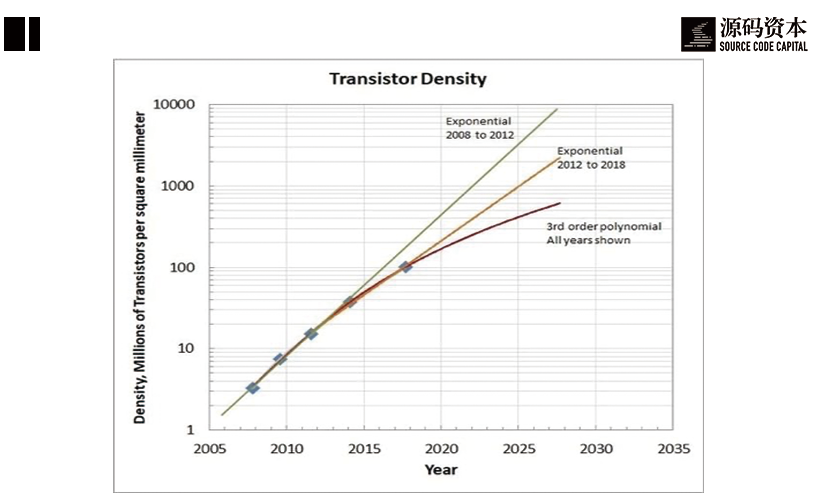

随着晶圆厂对先进制程投入的放缓,摩尔定律逐步失效:

图片来源:网络

“后摩尔时代”计算芯片的发展方向

从上一节的分析可以看出,“摩尔定律”首先是一条经济上的定律,然后才是工程科学方面的定律。晶圆厂维持摩尔定律,带来芯片集成度翻倍,成本减半,在系统集成商的角度就是性能翻倍,器件集成度翻番。用户端体会到的就是,到手的产品越来越好用,功能越来越强大,比如手机从大哥大到功能机,再到智能机。用户可以通过购买更先进的处理器,从而获得比购买处理器投入更多的生产效率,或者更好的用户体验;处理器生产商则通过赚到的钱,投入到技术研发生产更先进的处理器;更先进的处理器吸引更多的用户购买,如此往复。随着行业的发展,先进制成迭代一代的时间维持在18个月左右:如果太慢了,市场饱和,消费者没有换新品的动力,反过来削弱芯片厂和晶圆厂的盈利能力;太快了,技术进步还没法跨越上一代的积累,也没有*化上一代芯片的盈利能力,造成投入上的浪费。

摩尔定律所蕴含的商业规律:

如果维持摩尔定律的成本相对恒定,或者是不断有更多的新用户付费来摊薄芯片的研发和生产成本,摩尔定律背后的商业规律可以一直运行下去。但随着智能手机等智能终端的渗透率逐渐饱和,以及先进制成所需要的投入成本呈指数级增加,维持摩尔定律,对于芯片厂商和晶圆厂来说变得越来越不划算。

然而物联网、云、大数据、人工智能等新技术的发展,对于数据处理数据的需求并没有减弱,尤其是人工智能,需要对大量的图像、文本数据进行处理。为了解决数据增长和算力增长之间的不匹配,芯片设计师们开始寻找新的思路,其中两种有代表性的方向是:1)针对AI算法设计高效的并行计算架构;2)针对应用场景优化软硬件一体的解决方案。

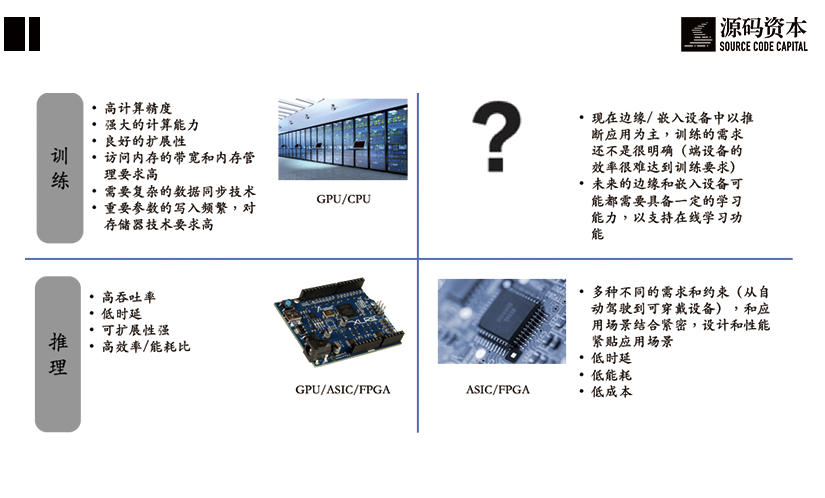

先看AI芯片,目前主流的AI算法主要是深度学习算法, 其底层的算子涉及到大量的并行计算。在不同的场景下,对于AI芯片又有不同的要求:

图片来源:网络

与用于通用计算的CPU相比,AI芯片是专才,擅长并行处理乘加运算。打个比方,CPU更像是一名大学教授,可以处理各种复杂的问题,而AI芯片是100个小学生,不能接受复杂的指令,但在乘加这类简单运算上,100个小学生加起来的计算效率,远大于一名大学教授。由此可见,AI芯片的设计思路是通过架构上的创新,增加并行乘加运算的效率,而不仅仅依靠制成的迭代提升计算能力。

AI芯片解决的主要问题,就是如何在单位时间内,高效的处理尽量多的乘加运算。一个“好”的AI芯片,需要在以下几个维度上下功夫:

高吞吐:吞吐率=模型QPS(query per second),单位时间能完成的模型inference次数,越高表示单位时间内做的推理次数越多。

低延时:模型输出-模型输入的时间差,延时越低越好。

计算资源利用率高:指的是在相同的计算单元的情况下,运行AI模型调动的有效的计算单元,调动计算单元的多少,和芯片设计的指令集与资源调度系统有关,同样的计算资源下,计算资源的利用率越高越好。

高效的片间互联:实际应用场景的AI模型往往需要跑在多张芯片上,对AI训练芯片不仅仅是停留在单芯片上,还需要片间的互联协议足够高效

高灵活性:是否有完善的深度学习的算子支持,可以运行的AI模型越多越好。

易使用:不需要retrain或者量化,直接运行已经训练好的模型。

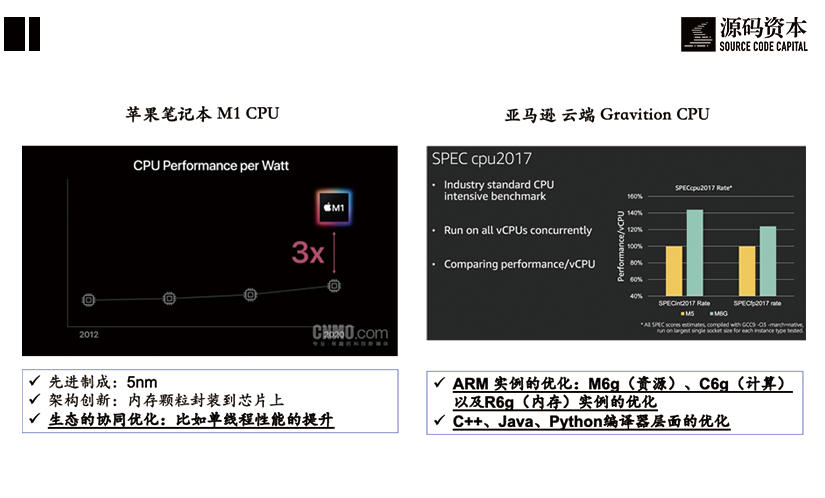

第二个思路是针对应用场景做软硬件一体的优化方案,从而*程度上发挥出硬件的潜力。典型的案例有苹果新发布的笔记本电脑,和亚马逊AWS的服务器。

苹果2020年最新发布的笔记本电脑搭载了自家研发的M1 CPU。除了应用了*进的制成技术(5nm)以及内存颗粒封装到芯片上这种架构创新外,与之前Intel的CPU不同的是,苹果的自研CPU针对自家的iOS做了深度的定制优化,在运行程序时的性能更强,相应的,用户端有更流畅的使用体验。

2002年,亚马逊的AWS推出了搭载自研Gravition CPU的云服务。基于 Graviton2 的 Amazon EC2 T4g、M6g(资源)、C6g(计算) 和 R6g(内存) 实例,为各种工作负载提供高达 40% 的性价比提升。基于ARM精简指令集的Gravition CPU 与基于复杂指令集的Intel x86 CPU相比,更加适合异构计算。

摩尔定律带我们的启示

距离“摩尔定律”的提出(1965年),已经过去56年了,站在今天这个时点回顾,我们会发现摩尔定律已经不能再准确地描述半导体先进制程的迭代速度了。而这背后蕴含的经济规律是:维持先进制成迭代需要的成本,逐渐超过他所带来的价值,因此先进制程迭代速度的放缓,也是顺理成章了。

然而另一方面,先进制成工艺发展的放缓,并不意味着计算芯片性能发展的放缓。我们依然能看到诸如增加AI计算能力、针对场景优化的垂直一体化整合等设计思路,推动计算芯片性能的不断进步,给用户带来各方面体验的提升。

对于中国芯片行业而言,摩尔定律逐步失效,某种意义上,是一种利好,它意味着国际上*玩家脚步的放缓,给了中国芯片产业追上来的机会。实际上,先进制成的主要应用领域是在消费电子,28nm/40nm的制成工艺、300nm尺寸的晶元,已经可以满足绝大部分*、工业场景的需求。随着国产28nm光刻机等一批关键芯片制造设备在未来1-2年内逐步落地,中国将在成熟制成工艺上实现芯片产业链的自主可控。