光刻机一直是半导体领域的热门话题。

从早期的深紫外(DUV)光刻机起步,其稳定可靠的性能为半导体产业的发展奠定了坚实基础;到后来的极紫外(EUV)光刻机以其独特的极紫外光源和更短的波长,成功将光刻精度推向了新的高度;再到如今的高数值孔径(High-NA)光刻机正式登上历史舞台,进一步提升了光刻的精度和效率,为制造更小、更精密的芯片提供了可能。

尤其是随着ASML High-NA EUV光刻机的问世,这一目前世界上*进的芯片制造设备,显著提升了芯片的晶体管密度和性能,这对于实现2nm以下先进制程的大规模量产至关重要。

在此形势下,英特尔、台积电、三星、SK海力士等晶圆制造大厂伺机而动,争相导入或宣布High-NA EUV光刻机市场进展,预示着半导体行业将迎来新一轮的技术革新和竞争高潮。

01 英特尔:时运不济

在半导体巨头中,英特尔是率先向ASML订购新型High-NA EUV设备EXE:5000的企业。

早在2023年12月,英特尔就拿下了全球首台High NA EUV光刻机,并于今年4月宣布其已在位于美国俄勒冈州希尔斯伯勒的Fab D1X研发晶圆厂完成世界首台商用High-NA(0.55NA) EUV光刻机的组装工作,目前已进入光学系统校准阶段,并计划在其18A(1.8nm)和14A(1.4nm)节点上使用。

今年8月,英特尔又宣布成功接收全球第二台价值3.83亿美元的High-NA EUV光刻机,目前在俄勒冈州的晶圆厂已经顺利完成安装调试。

ASML早些时候曾表示,2nm光刻机近期的产能只有10台,预计到2028年才能每年生产20台。值得注意的是,这10台最新光刻设备,公开资料显示有6台已被英特尔拿下。

可见,在*进光刻机的导入进展上,英特尔取得了遥遥*的优势。

常言道“吃一堑,长一智”,而英特尔之所以如此积极的选择High-NA EUV设备,实际上很大原因在于其此前在EUV上跌过的跟头。

Tick-Tock模式溃败、错失EUV技术窗口

众所周知,英特尔与ASML合作了数十年时间,推动了光刻技术从193nm浸没式光刻技术发展到EUV,但出于成本考虑,英特尔时任CEO不愿采用昂贵的ASML EUV光刻机,选择不在其10nm工艺中使用该技术,而是使用DUV光刻机进行四重图案化,结果导致英特尔在良率方面遇到了重重困难。

回顾历史能看到,2011年英特尔首发了22nm FinFET工艺,远超当时台积电、三星的28nm,技术优势可谓遥遥*。然而从14nm节点开始,英特尔接连遭受重创。

2014年,英特尔和三星都实现了14nm制程芯片的生产,可到2017年,台积电已经推进到10nm、7nm工艺,英特尔却因为不愿意采用最新的EUV光刻技术,导致其原计划在2016年大规模量产10nm芯片直到2019年才实现量产,比台积电推出时间晚了两年半,而其7nm芯片更是直至2022年才推出。

实际上,除了没能把握住EUV技术之外,英特尔代工的衰退与其“Tick-Tock”战略也脱不了关系。

英特尔前任CEO保罗·欧德宁对于芯片制造曾提出“Tick-Tock”战略,即在Tick年(工艺年)更新制作工艺,Tock年(架构年)更新微架构,相当于每两年一次工艺制程进步。但同期,为推行“高效管理”、“成本节约计划”,英特尔裁员2万人,大量参与下一代芯片工艺和架构研发的工程师被裁撤,导致“Tick-Tock”模式难以持续,14nm芯片延迟一年才推出,10nm芯片更是几番推迟。

英特尔像挤牙膏一样对芯片技术进行微小的年度更新,那些年一度被大家讥讽为“牙膏厂”。

随着Tick-Tock模式的崩溃,以及错失EUV早期技术窗口,英特尔开始逐渐掉队。

与此同时,台积电和三星从ASML大量采购EUV设备,不断缩小芯片的制程尺寸,提高芯片的效率和性能,大大提升了在晶圆代工领域的竞争力。在先进制程上,英特尔被台积电、三星远远甩在了身后。

更严重的是,生产工艺落后、产品竞争力下滑,不仅影响了英特尔的代工业务,也使其台式机芯片和服务器芯片的市场份额不断被蚕食。

可谓,牵一发而动全身。

02 英特尔自救,前路何在?

因此,痛定思痛后的英特尔,率先对High-NA EUV光刻机展开了攻势,试图追回被拉开的差距。

上面提到,2024年4月,重达150吨的巨大设备被安装在英特尔位于美国俄勒冈州的研究设施里。

这也是在英特尔CEO Pat Gelsinger提出“IDM 2.0”战略后,迅速重新聚焦于尖端制程工艺的提升,提出了四年五个工艺节点的计划,希望在2025年凭借Intel 18A实现对于台积电2nm工艺的追赶和超越。

与此同时,英特尔希望通过率先采用High NA EUV光刻机来实现对于台积电等竞争对手的持续*。英特尔的目标是在2026至2027年间实现Intel 14A制程技术的量产,并在此基础上进一步提升制程技术。最终在2030年前实现英特尔代工业务实现收支平衡的运营利润率,并成为全球第二大晶圆代工厂。

目标指引下,英特尔正在不断加强代工基础设施建设,计划未来5年投资1000亿美元扩大先进芯片制造能力。同时将投资约300亿欧元在德国马格德堡建设两家半导体工厂。这些投资计划将使英特尔芯片代工能力大幅提升。

然而,战略愿景很美好,但现实却很残酷。

尽管英特尔雄心勃勃,但由于四年五个节点及路线演进、生态构建和产能扩建等巨额的投入,英特尔披露其代工业务去年营收同比下降31.2%至189亿美元,经营亏损70亿美元,同比扩大34.6%。

2024年有可能将是英特尔芯片制造业务经营亏损最严重的一年,今年Q1财报显示,该业务运营亏损25亿美元,几乎是上一季度的两倍;Q2亏损更是达到28.3亿美元,代工亏损额不断扩大。

据研究机构TrendForce集邦咨询数据,2024年二季度,英特尔并未进入全球晶圆代工厂营收前10名。在过去几年里,英特尔曾经在2023年第三季度短暂上榜,市场份额仅为1%。

这意味着,IFS三年来无法真正托举起英特尔以尖端芯片制造重塑行业地位的目标,同时作为美国本土*有能力能承担起前沿代工行业承担着的角色,英特尔也无法扛起时代重任。

据心智观察所报道,美国半导体咨询公司D2D Advisory总裁Jay Goldberg也特别指出:“英特尔代工面临的真正挑战,还在于他们的经济模式中必须要拥有更多的客户,以支持不断推进其制造流程所需的研发。必须加大外部客户需求,将收入规模增加一倍,以支持保持在摩尔定律的轨道上继续前进。”

不难看到,英特尔目前已陷入到两难境地,业绩持续下滑,2024年甚至由盈转亏,股价暴跌将近60%,市值几度跌破千亿美元,成为标普500指数中表现最差的科技股之一。

面对危机,英特尔在内部信上表示,将进一步分离芯片制造和设计业务,这是该公司解决50年历史上最严重危机之一的一系列新措施的一部分。

根据英特尔此前公布的预测数据显示,分拆晶圆制造业务后,2023年可以节省30亿美元成本,2025年将节省 80-100亿美元成本。同时也推迟德国和波兰建厂计划2年;马来西亚建厂则会完成,但正式启用时间则视市况与产能利用率而定。

在英特尔继续紧急行动执行上个月宣布的计划的同时,英特尔也在努力谨慎管理现有的现金,以有意义地改善资产负债表和流动性。其中就包括出售部分 Altera的股份,并推动其独立IPO;产品研发策略方面,也规划将简化x86产品组合。这也是英特尔多次公开讨论的计划。

今年8月,英特尔甚至还被曝出正在考虑分拆其产品和代工业务。值得一提的是,在传出或分拆其晶圆业务之后,英特尔股价曾反弹9%以上,可见投资者对芯片代工业务有多失望。

处在低谷中的英特尔就是美国芯片制造业的一个缩影,成本、技术、资源、IDM身份等,都在制约英特尔野心勃勃的芯片代工计划。但尽管业界也有放弃芯片代工的可能性探讨,尽管芯片代工业务持续的亏损已经让资本市场不满意,但这也是为数不多能拯救英特尔于水火的关键布局。

英特尔没有选择,只有抓住任何的可能性,硬着头皮上。

因此,英特尔需要最尖端的High-NA EUV光刻机作为生产和营销工具,以宣示自身在3nm以下的研发制造实力且尝试壮大客户群,但High-NA EUV光刻机作为新机,又让英特尔不得不冒着设备折旧和量产摊销成本的压力以平息外界质疑。

从行业竞争的持续以及芯片代工“重资产、长周期”的产业属性来看,英特尔还有诸多硬仗要打。尤其是在英特尔开启公司史上*转型以自救的处境下。

英特尔过去也有过从困境中复苏的经历。1980年代在日本企业的攻势下,英特尔撤出了DRAM,把经营资源集中于CPU,席卷了个人电脑市场。

正如基辛格所述:“这是英特尔四十多年来最重要的转型。自从内存过渡到微处理器以来,我们还没有尝试过如此重要的事情。我们当时成功了,我们将迎接这一时刻,并在未来几十年内打造更强大的英特尔。”

但英特尔的种种自救,仍需要时间检验。

03 三星电子,陷代工阴霾

今年8月,在“2024年光刻+图案学术会议”上,三星电子表示为了在与英特尔、台积电等全球半导体竞争对手的“芯片战”中保持竞争力,公司正在积极参与技术开发,最早将在2024年底到2025*季度之间引进公司首台High-NA EUV设备“EXE:5000”,并有望在2027年实现该技术的全面商业化。

据悉,该设备可能被放置在位于华城园区的半导体研究所(NRD),预计将用于代工业务,以进一步提升在先进节点领域的竞争优势。

实际上,三星芯片代工在早年占据了*优势。2007年乔布斯发布*代iPhone时,使用的正是从三星采购的ARM架构芯片。后续搭载于iPhone 4、iPhone 4s、iPhone 5、iPhone 5s/5c身上的A4、A5、A6、A7芯片也均由三星代工,那时候还没有台积电什么事。

直到2011年,因为三星自己也从事手机芯片和手机终端研发和销售业务,如此一来就与苹果在智能手机市场上有了竞争关系。双方互相拉扯,直到2018年6月才达成和解。

在这个过程中,苹果也开启了“去三星化”进程。2014年推出的A8芯片,全部转由台积电代工。台积电能顺利从三星手中抢到苹果的订单,一方面是苹果急着寻找可替代的代工商,给台积电制造了很大的机会。另一方面是台积电在20nm工艺上取得重大突破,良品率大幅提升,而三星的20nm工艺突然掉链子,关键问题迟迟无法解决,良品率满足不了苹果的要求。正是这样的天时地利,让台积电成功抱到了苹果这条大腿。

反观三星,大客户被抢之后,决定不搞20nm,选择直接从28nm跳到14nm,对台积电的16nm形成反超。所以,在2015年的A9芯片上,苹果又重新分给三星一部分订单,于是出现台积电代工和三星代工两种版本。理论上,三星14nm表现应该是优于台积电16nm,但消费者的口碑却完全相反,很多人都担忧买到三星代工的版本。

这次的失利,让三星彻底失去苹果的代工订单,苹果公司之后的芯片均由台积电代工,制程也从2015年的16nm,稳步提升到4nm。

与此同时,高通也险些在三星代工中跌了跟头,骁龙8+Gen1紧急转为台积电4nm代工,才强行挽回了高通的口碑和市场地位。

在芯片代工赛道上,三星具有起步优势,但奈何中期连续多次失利,才让台积电一步步实现反超,直至今日的大幅*。然而,三星也清楚自己与台积电之间存在这技术差距,所以想要对台积电形成反超,就必须拿出更强的“杀手锏”。

于是,三星几乎把追赶台积电的全部希望都押注在3nm工艺上。2023年,三星率先推出3nm制程工艺,采用更加先进的GAA(环绕栅极晶体管)技术,*于台积电的FinFET技术。

可以说,3nm相当于三星最后的“背水一战”,如果能一举追赶台积电,或许未来有机会形成双雄争霸的局面。

然而从市场进展来看,三星3nm工艺在良率方面面临挑战,这导致了一个很尴尬的局面,即三星的3nm芯片,虽然比台积电先推出,但是成本却比台积电高出很多,性能表现也存在差距。据悉,三星第二代3nm制程工艺良品率不稳定,自家Exynos2500良品率都不足20%,三星Galaxy25系列手机全系搭载骁龙8Gen4处理器,放弃自研Exynos2500版本,原因是体验差异太大。

与台积电差距拉开之后,给三星下订单的客户越来越少。

过去高通先进制程的芯片一直都是三星*代工,结果在5nm芯片之后,高通也将先进制程的芯片订单交给了台积电;现如今,苹果的A17、A18系列芯片,全部采用台积电的3nm工艺制造;高通的3nm芯片和联发科的天玑9400等也全由台积电代工;连英伟达、AMD、特斯拉的3nm芯片,都是台积电代工,包括现在英特尔的订单也给了台积电。

在芯片制造上,台积电一家拿下了全球60%以上的市场份额,3nm的芯片制造几乎拿下100%的份额,而7nm以下的芯片制造,拿下了90%的份额。第二大晶圆厂三星的市场份额仅为11.5%。

据《朝鲜日报》消息,三星已经将平泽2厂,3厂的4nm,5nm和7nm生产线关闭了30%产能。预计到2024年底,还将继续关闭产能直到50%。这一举措显然是为了应对全球科技巨头如英伟达、AMD及高通等未能给予三星电子大规模订单的现状。

有行业专家强调,一旦设备关闭,恢复正常运营是一个漫长的过程。通常情况下,即使在需求低迷时期,公司也会降低利用率,而不是全面停工。然而,三星近30%的先进工艺设备闲置是前所未有的。

2024年第三季度,三星包括晶圆代工和系统LSI等非內存部门亏损金额超过1万亿韩元。此外,三星3nm制程的良率持续处于低位,也一直没有获得大客户的采用,近期还将美国得州泰勒市先进代工晶圆厂量产时间延后到2026年。

综合来看,这样的差距,让三星在3nm时代,想要超越台积电的梦想彻底破灭了。

因此,三星引进High-NA EUV光刻机的消息,意味着其将与英特尔和台积电在下一代光刻技术上展开更为激烈的竞争。

三星计划在2025年量产2nm制程,并逐步扩展到其他应用领域。比如,2025年首先用于行动领域,2026年扩展到HPC应用,2027年再扩展至汽车领域。三星的2nm制程节点采用了优化的背面供电网络技术,以降低供电电路对信号电路的干扰。

这一发展标志着三星首次涉足High NA EUV技术。此前,三星电子曾与IMEC合作进行电路处理研究。三星计划利用自己的设备加速先进节点的开发,并设定了到2027年实现1.4nm工艺商业化的目标,这可能为1nm生产铺平道路。

此外,为了实现全面商业化,三星还正在积极构建相关生态系统。

据悉,三星电子已购买了雷射技术公司的High-NA EUV掩膜检查设备"Actis(ACTIS) A300"。预计在三星电子内部完成ASML的EXE:5000安装后,将从明年上半年开始正式引进。同时与电子设计自动化(EDA)公司合作设计新型光罩,包括用于High-NA EUV的非直线(Curvilinear)掩膜电路绘制方法,以提高晶圆上印刷电路的清晰度。此次合作涉及半导体EDA工具全球*Synopsys等公司。

除了ASML、雷射技术公司、Synopsys之外,三星电子预计还会与JSR等光刻胶公司、将光刻胶涂在晶圆上的跟踪设备"Number One"东京电子等多家公司合作,为High-NA时代到来做准备。据悉,三星电子正通过这样的生态系统建设工作,准备在2027年正式商用High-NA。

三星电子的晶圆代工业务正站在一个关键的十字路口,其生死存亡,似乎全系于2nm芯片制程技术的量产之上。这不仅是技术上的飞跃,更是三星晶圆代工业务能否重获新生的关键。

然而通往成功的道路从来都不是一帆风顺的。三星在推进其技术蓝图的过程中,不得不面对一系列严峻的挑战:

首先是技术层面的难题,先进制程的良率问题一直是悬在半导体厂商头上的达摩克利斯之剑。三星的3纳米制程就因良率低迷、可靠性存疑而未能达到量产标准,这无疑给其晶圆代工业务蒙上了一层阴影。

更糟糕的是,市场的反应也并未如三星所愿。尽管三星努力提升技术实力,但在客户心中,其晶圆代工业务的可靠性和竞争力仍显不足。面对台积电等强劲对手,三星在争取高端客户方面显得力不从心。这种市场困境,进一步加剧了三星的财务压力。据估算,三星晶圆代工业务在第三季度恐将亏损数千亿韩元,这是对三星管理层的一次重大考验。

面对内忧外患,三星高层不得不做出一系列艰难的决定。

根据研究公司Statista的数据,尽管三星多年来一直努力挑战台积电,但三星在代工制造市场的份额在过去五年里下降了8个百分点,2024年第二季度,三星占据全球代工市场份额的11.5%,而台积电占据62.3%的市场份额。

三星市场份额的下降凸显了其在掌握先进芯片制造技术方面面临的技术挑战,在代工业务上投资过多,既没有获得足够的客户,也没有稳定生产工艺,这进一步导致了三星目前的危机。

综合来看,半导体行业本身是技术快速迭代与市场变幻莫测的领域,三星必须保持足够的敏锐度,以应对未来的变化。如何在快速变化的市场中找到适合自身发展的道路,是三星当前亟待解决的问题。

04 台积电“有条不紊”,赢下“谈判游戏”

作为半导体行业的*,台积电在过去的30多年中立下了赫赫战功。过去多年来,在面对三星和英特尔带来的巨大挑战和压力时,台积电审时度势并采取有效的措施,成为了世界*大芯片代工企业。

如今,即使行业头部半导体企业纷纷争夺High-NA EUV设备,台积电似乎并不急于加入这一行列。

此前,谈到何时导入High-NA EUV设备,台积电资深副总暨副共同营运长张晓强接受外采访时透露,台积电胸有成竹,不会因为对手们抢先添购设备而盲目扩大采购,仍采稳扎稳打方式布局先进制程,迎接挑战。

然而,近期有消息报道,台积电预计将于今年年底从ASML接收首批全球*进的芯片制造设备——高数值孔径极紫外(High NA EUV)光刻机。这一消息标志着台积电在半导体制造领域再次迈出了重要一步。

有趣的是,台积电前期以成本为由,迟迟不肯接受High NA EUV。早些时候,台积电CEO魏哲家缺席“台积电技术研讨会2024”,而是前往荷兰埃因霍温的ASML总部洽谈设备。

如今看来,这有点像台积电的谈判游戏,也许是在与ASML争取更好的条件。

传闻魏哲家亲自与ASML谈判并达成了一项协议,通过购买新设备和出售旧型号相结合的方式,将整体价格降低了近20%。ASML同意以折扣价向台积电出售High-NA EUV设备的原因主要是因为台积电是其超级VIP客户,ASML给予了很大的让步。这一让步包括全力协助台积电进机、调校与技术支援等,以加速上线时间点。

因此,台积电的态度也发生了戏剧性的转变,由原先对新款High NA EUV光刻机价格的犹豫,转为积极寻求合作。

据悉,台积电则预计将在本季度在其位于中国台湾新竹总部附近的研发中心安装新的High NA EUV光刻机。短期内,台积电计划将High NA EUV光刻机主要用于研发,以开发客户推动创新所需的相关基础设施和模式解决方案。

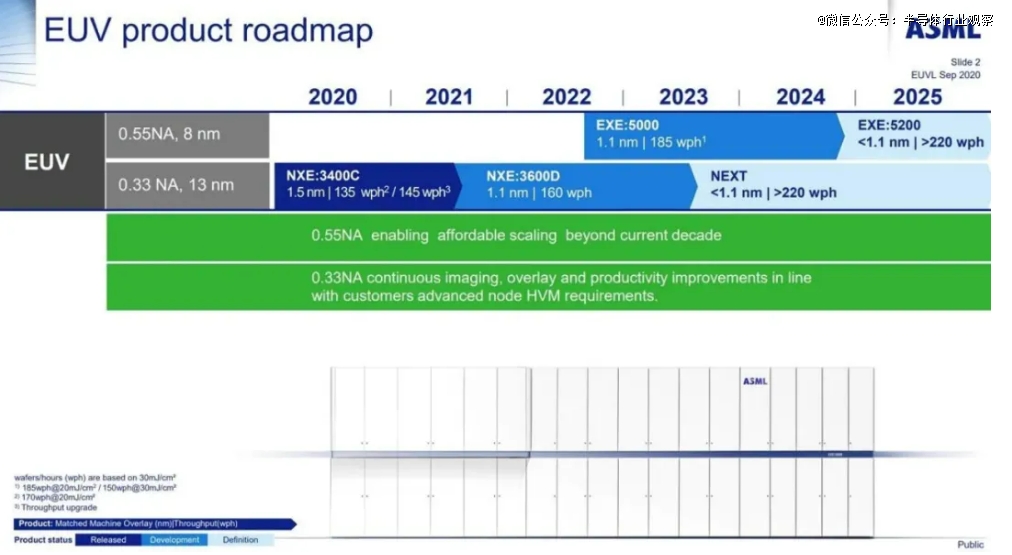

根据ASML的路线图,*代的High-NA EUV光刻机TWINSCAN EXE:5000或许主要是被晶圆制造商用于相关实验与测试,以便公司更好地了解High-NA EUV设备的使用,获得宝贵经验。实际量产将会依赖于2024年底出货的TWINSCAN EXE:5200。

台积电即将推出的N2(2纳米级)和A16(1.6纳米级)工艺技术将完全依赖于传统的EUV设备,这些设备的光学元件具有0.33 NA。业界预计,台积电最早可能在2028年或更晚的A14(1.4纳米级)工艺技术中采用0.55 NA EUV工具,尽管目前公司尚未对此进行官方确认。

与竞争对手相比,台积电可以通过持续的生产实践积累宝贵的经验数据与优化工艺,从而难以构建起“订单驱动-技术迭代-再获订单”的良性循环体系。换言之,台积电有着极为庞大的优质客户群协助他们调试各种设备bug,这恰恰是三星和英特尔所缺少的。

台积电布局策略:无宝不落

笔者此前曾提到,从三巨头布局策略和方式来看,台积电往往被认为是一个保守技术开发者,其倾向于确保新技术的成熟和可靠性,然后再进行部署,而不是急于将新技术推向市场。

从实际的市场表现来看,台积电此举可以降低技术失败的风险,提高其芯片的产量和质量,从而确保客户的满意度。

例如,三星在2018年开始在其7nm工艺中使用EUV光刻机,然而台积电选择等待。直到EUV工具的稳定性和成熟性得到确认,以及相关问题得到解决或至少得到确定,才在2019年的N7+工艺中开始使用EUV。

此后,在FinFET向GAA工艺的过渡上,台积电依旧重操这一模式。凭借工艺*性和生产良率上的技术优势和积累完全有实力与采用GAA技术架构的三星抗衡。

在英特尔大力押注的BSPDN背面供电技术上,台积电依旧不紧不慢,计划将在2026年底才开始大规模生产的N2P上加入。

这种谨慎的方法有助于台积电确保其制程技术的稳定性和可预测性,从而提供高质量的芯片给其客户。

但从先进封装领域来看,台积电则一改常态,积极布局率先落地,在先进制程与先进封装的组合拳下,为其带来了新的增长浪潮。

在这张弛有度的策略下,充分凸显着台积电的战略哲学和独到眼光。在其看准的蓝海赛道,台积电始终敢为人先,无论是十年前率先试产16nm FinFET制程技术超越英特尔,还是五年前部署先进封装收获如今的AI红利,台积电都精彩演绎了所谓凤凰无宝不落。

而在其保持较大优势的先进制程领域,纵然面对三星和英特尔的步步紧逼,台积电没有选择盲目激进,反而采取了先观察再跟随的策略,在做好充分的准备和规划后“亦步亦趋”,凭借自身强大的产能、良率和客户基础的基本盘优势,维持不败之地。

05 SK海力士发力 High NA EUV,押宝HBM

此外,在存储领域,SK海力士的首台High NA EUV光刻机“EXE:5200”则有望2026年引入,旨在支持其先进DRAM产品的量产。这一举措进一步彰显了半导体行业对于先进制程技术的持续追求和投入。

2023年,SK海力士就曾单独组建了一个团队,专门开发High-NA EUV技术。

SK海力士作为HBM领域巨头,正不断加大对High-NA EUV技术开发的内部投入,积极扩大相关研发团队。尽管关于设备安装的具体晶圆厂位置及额外投资方向等信息尚未公开,但业界普遍预期,该技术将迅速应用于0a(个位数纳米)DRAM的规模化生产,以进一步提升产品竞争力。

06 写在最后

7nm以下的世界是另类冒险家的乐园,台积电,三星和英特尔的竞合关系变得愈发微妙。

根据光刻机之“瑞利公式”,光刻工艺的提升在过去几十年来一直在多维度全面出击,即不断优化曝光波长、数值孔径以及工艺因子。但目前曝光波长的缩短、数值孔径(NA)的增加都已经逼近了物理和成本综合考量的极限。

如今距离摩尔定律的极限越来越近,行业几乎走到了隧道尽头,2nm及接下来几代工艺节点将会是芯片巨头抢滩的关键。

在全球范围内,台积电、英特尔和三星等半导体巨头之间的竞争正在升温,它们竞相获得2nm以下工艺的High NA EUV设备。英特尔于2023年12月率先获得该设备,台积电于2024年第三季度紧随其后。尽管三星的订单来得晚,但实现稳定的生产可能是决定行业*地位的关键因素。

但芯片代工的竞争,不仅仅是技术的竞争,更是客户、品牌、良率、产能等各方面的综合竞争。不知道,英特尔和三星能否在新市场的黎明期抓住重新崛起的机会。如果失败,台积电将继续独占鳌头。