提到晶圆代工,台积电*是首屈一指的行业“领头羊”。

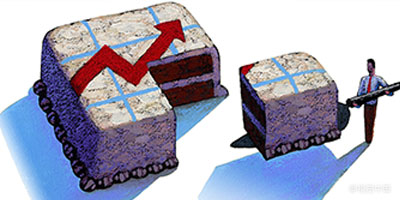

而如今,随着摩尔定律放缓、AI浪潮推动,先进封装作为提升芯片性能的关键技术路径,正被进一步推至半导体行业的前沿。

根据Yole最新发布的《2024年先进封装状况》报告,预计2023-2029年先进封装市场的复合年增长率将达到11%,市场规模将扩大至695亿美元。

市场潜力之下,前后道头部厂商纷纷抢滩,积极投资先进封装技术。

在这个过程中,我们可以明显观察到,传统封测厂(OSAT)在市场竞争中逐渐处于一定的落后位置,许多原本专注于代工的企业也开始进军先进封装市场,从台积电的CoWoS,到英特尔的EMIB,再到三星的X-Cube,各类2.5D与3D封装陆续涌现并走向成熟,在封装这片蓝海中,掀起了犹如千帆竞逐的热潮。

其中,台积电逐渐逼近先进封装市场首位。

近日,研究机构ALETHEIA断言,台积电不仅是先进制程领头羊,先进封装明年也将起飞,有望成为*封装服务供应商,堪称半导体产业*的存在。

得益于Chiplet架构加速采用,驱动2.5D/3D封装技术进展,台积电2026年先进封装产能将是2023年的十倍,2027年更会达到2023年的15倍。

可以预见,如今后摩尔时代,先进封装备受资本与产业瞩目。台积电作为执牛耳者,更是在大力入局先进封装,技术创新、产能迭代异常活跃。

01 台积电,引*进封装市场

回顾过去多年发展历程能看到,台积电推出了支持先进封装和开启异构集成新时代的技术战略。

早在2008年,台积电便成立集成互连与封装技术整合部门(IIPD)入局先进封装。

彼时,在金融危机的背景和影响下,台积电陷入了经营亏损、被迫减薪裁员的困境。与此同时,28nm制程工艺环节,研发成本快速提升;台积电同时还面临三星、英特尔、格芯以及联电的强力挑战。

内忧外患下,张忠谋重新出山执掌台积电,同时请回已经退休的蒋尚义掌舵研发,开发先进封装技术进行差异化竞争。

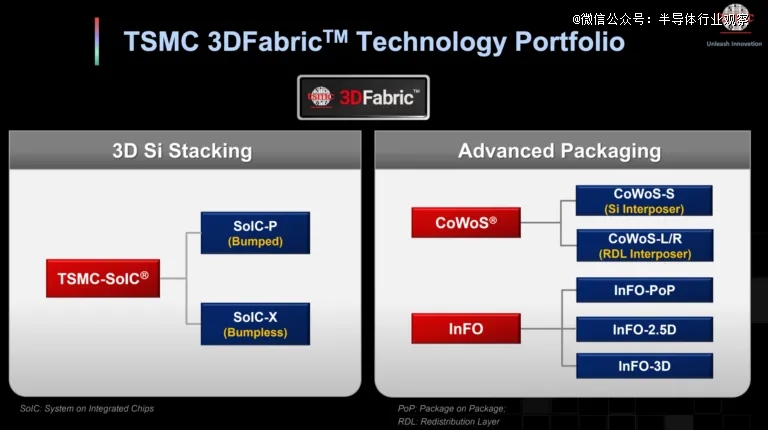

近年来,台积电每年资本开支中约10%投入先进封装、测试、光罩等,目前已形成2.5D封装CoWoS、扇出型封装InFO和3D封装SoIC等技术阵列。

笔者在一文中曾有过介绍:2011年,台积电带来了*个产品——CoWoS,正是台积电独霸全球先进封装领域的秘密武器之一。

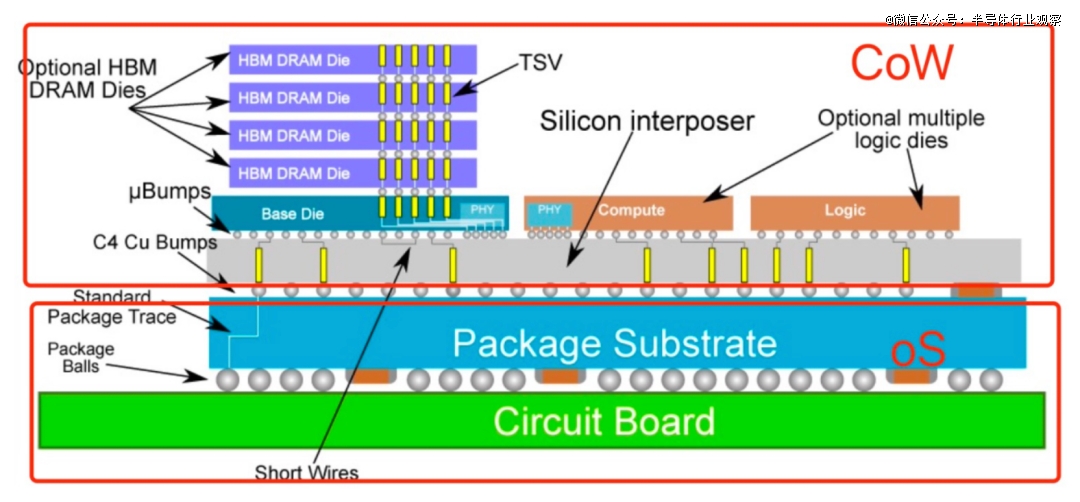

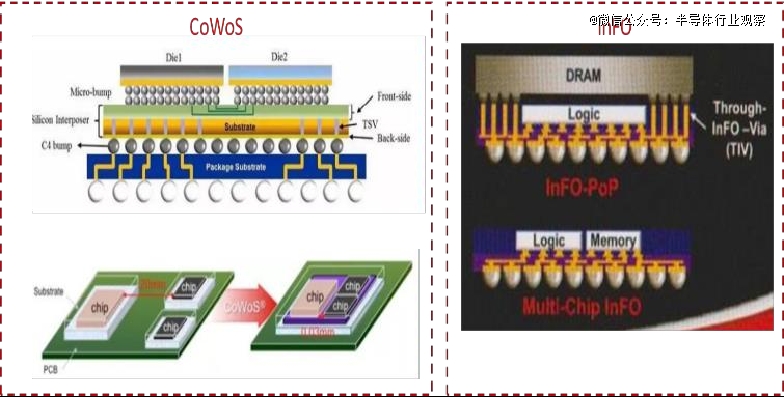

CoWoS(Chip On Wafer On Substrate)是一种2.5D的整合生产技术,由CoW和WoS组合而来:CoW就是将芯片堆叠在晶圆上(Chip-on-Wafer),而WoS就是基板上的晶圆(Wafer-on-Substrate),整合成CoWoS。

台积电CoWoS结构示意图

据悉,这是蒋尚义在2006年提出的构想。

CoWoS的核心是将不同的芯片堆叠在同一片硅中介层实现多颗芯片互联。在硅中介层中,台积电使用微凸块(μBmps)、硅穿孔(TSV)等技术,代替传统引线键合用于裸片间连接,大大提高了互联密度以及数据传输带宽。

CoWoS技术实现了提高系统性能、降低功耗、缩小封装尺寸的目标,从而也使台积电在后续的封装技术保持*。这也是目前火热的HBM内存、Chiplet等主要的封装技术。

根据不同的中介层(interposer),台积电“CoWoS”封装技术分为三种类型:

CoWoS_S:使用Si衬底作为中介层。该类型是2011年开发的*个“CoWoS”技术,在过去,“CoWoS”是指以硅基板作为中介层的先进封装技术;

CoWoS_R:它使用重新布线层(RDL)作为中介层;

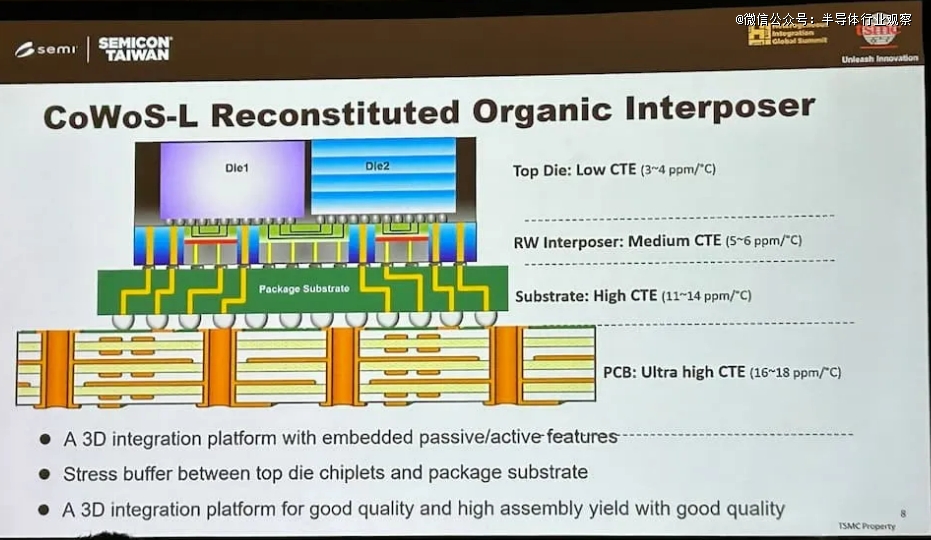

CoWoS_L:它使用小芯片(Chiplet)和RDL作为中介层,结合了CoWoS-S和InFO技术的优点,具有灵活的集成性。

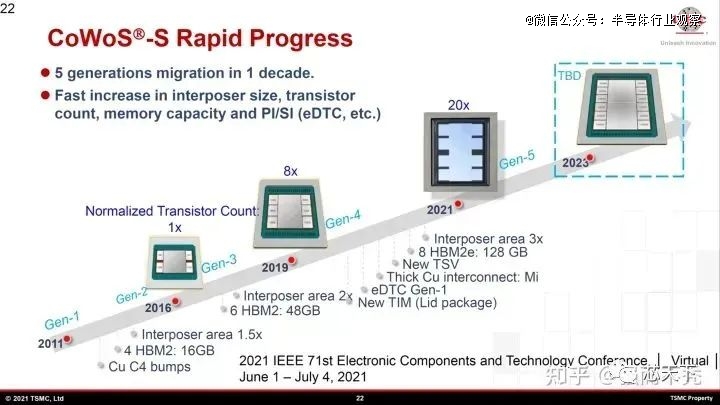

台积电通过早期的技术积累和大量成功案例,CoWoS封装技术目前已迭代到了第5代。

CoWoS 封装技术的路线图

然而,如今火热的CoWoS在刚推出时一度处境尴尬。

由于价格昂贵,台积电CoWoS封装只得到了FPGA大厂赛灵思的订单,这也是台积电先进封装项目组在2012年收到的*订单。

对此,台积电决定给CoWoS做“减法”,开发出了廉价版的CoWoS技术,即InFO技术。

InFO封装把CoWoS封装中的硅中介层换成了polyamide film材料,从而降低了单位成本和封装高度。这两项都是InFO技术在移动应用和HPC市场成功的重要标准。

得益于InFO技术的推出,当年苹果的iPhone7、iPhone 7Plus处理器,采用的便是InFO封装技术。这也成为台积电后来能独占苹果A系列处理器订单的关键因素。

而真正引爆CoWoS封装的产品是AI芯片。2016 年,英伟达推出*采用CoWoS封装的GPU芯片GP100,为全球AI热潮拉开序幕;2017年Google、英特尔产品相继交由台积电代工,采用CoWoS封装。

至此,因成本高昂而坐冷板凳多年的CoWoS技术迎来新局面,产能也相继扩充。

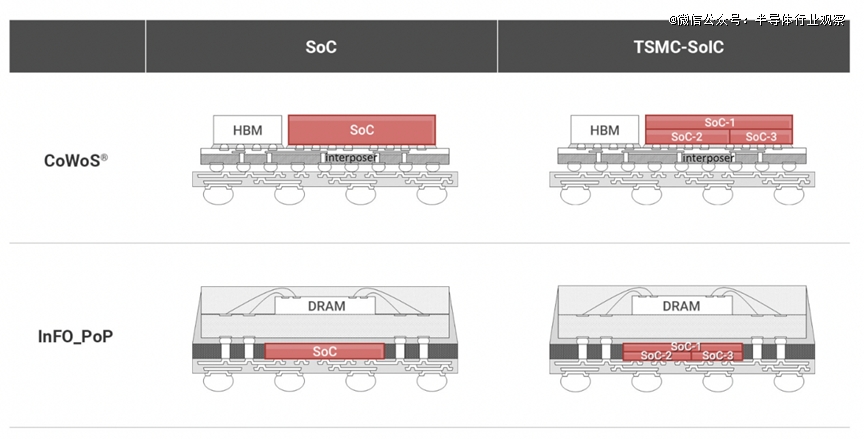

此外,台积电还公布了创新的系统整合单芯片多芯片3D堆叠技术——SoIC。

SoIC是一种基于台积电的CoWoS与多晶圆堆叠(WoW)封装技术开发的新一代多芯片堆叠技术,这两种方案在混合和匹配不同的芯片功能、尺寸和技术节点时提供了出色的设计灵活性。

SoIC的推出也标志着台积电已具备直接为客户生产3D IC的能力。相较2.5D封装方案,SoIC的凸块密度更高,传输速度更快,功耗更低。

2020年,台积电宣布将其2.5D和3D封装产品合并为一个全面的品牌3DFabric,进一步将制程工艺和封装技术深度整合,以加强竞争力。

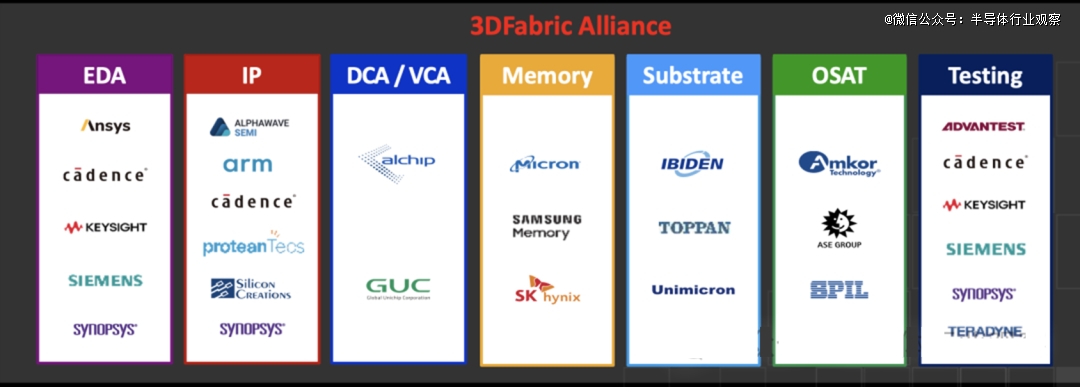

为了使所有这些封装技术在整个生态系统中发挥作用,台积电在2022年成立了3DFabric联盟,与包含EDA、IP、DCA/VCA、内存、OSAT、基板、测试7个环节的头部企业开展合作,旨在将其自有的封装技术标准化,以便提前抢占未来市场的主导地位。该组织还推动整个3Dfabric堆栈的工具、流程、IP 和互操作性的 3DIC 开发。

02 台积电先进封装技术,持续升级

在前不久的北美技术研讨会上,台积电详细介绍了其半导体和芯片封装技术的未来路线图。

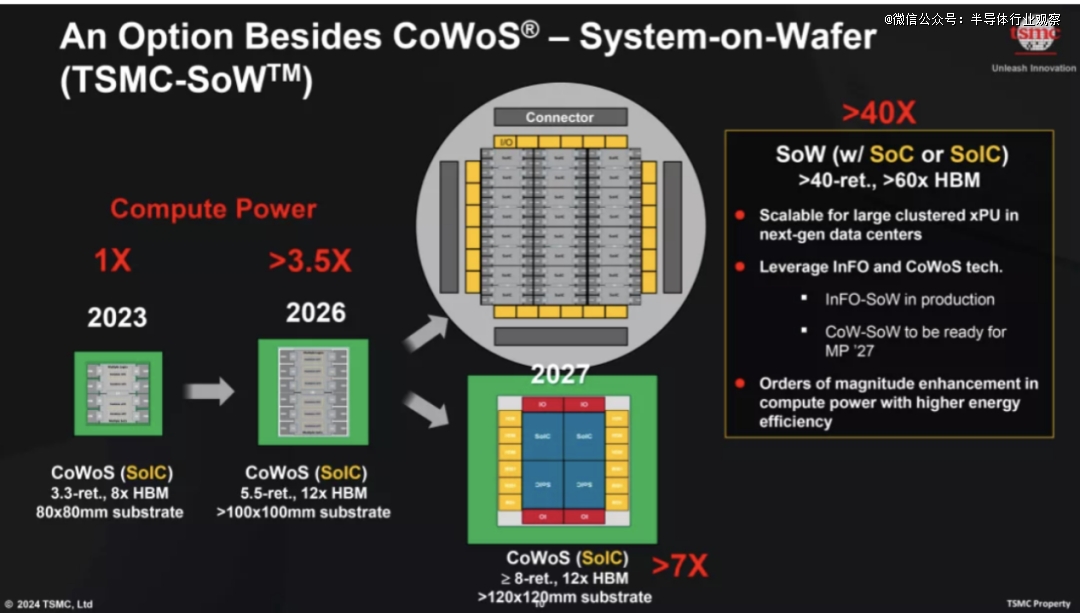

CoWoS技术迭代趋势

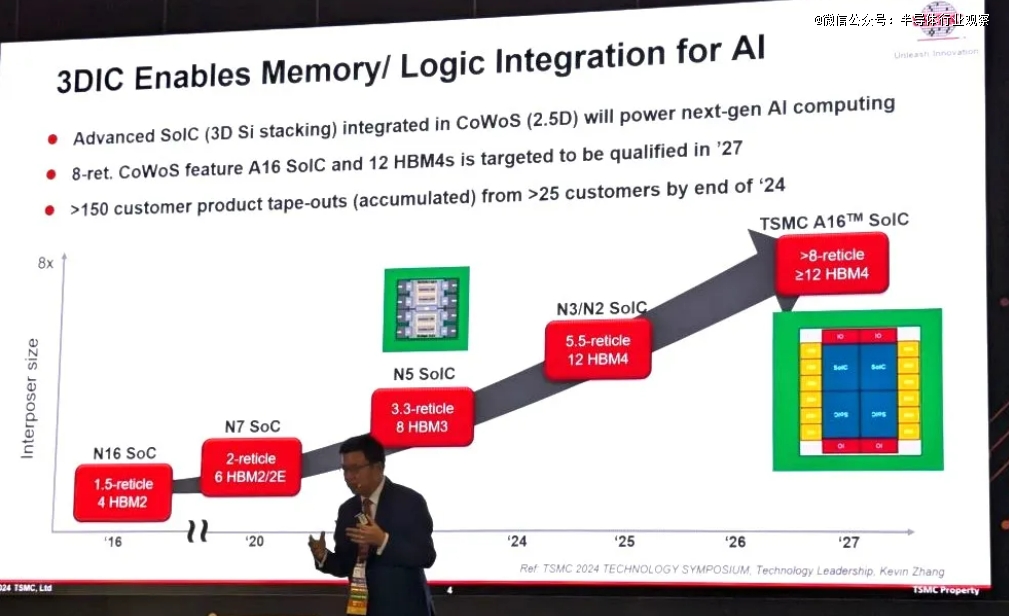

首先是CoWoS封装技术,当前的CoWoS迭代支持中介层(硅基层)的尺寸高达光刻中使用的典型光掩模的3.3倍。预计到2026年,台积电的“CoWoS_L”将使其尺寸增加到大约5.5倍的掩模尺寸,为更大的逻辑芯片和多达12个HBM内存堆栈留出空间。而仅仅一年后的2027年,CoWoS将扩展到8倍掩模版尺寸甚至更大。

在近日的专题演讲上,台积电高效能封装整合处处长侯上勇表示,作为能满足所有条件的*解决方案,台积电的先进封装重点会从CoWoS-S 逐步转移至CoWoS-L,并称CoWoS-L 是未来蓝图关键技术。

由于顶部晶片(Top Die)成本非常高,CoWoS-L是比CoWoS-R、CoWoS-S更能满足所有条件的*解决方案,且因为具有灵活性,可在其中介层实现异质整合,会有其专精的尺寸与功能。CoWoS-L可兼容于各式各样的高效能*芯片,例如先进逻辑、SoIC和HBM。

SoIC演进路线图

针对SoIC-X(无凸块)封装技术,台积电预计,到2027年,SoIC-X技术将从目前的9μm凸块间距一路缩小到3μm间距,将A16和N2芯片组合堆叠在一起,改进的混合键合技术旨在让台积电的大型HPC客户(AMD、博通、英特尔、NVIDIA等)能够为要求苛刻的应用构建大型、超密集的分解式处理器设计,大大提高组装芯片的带宽密度和产品性能。

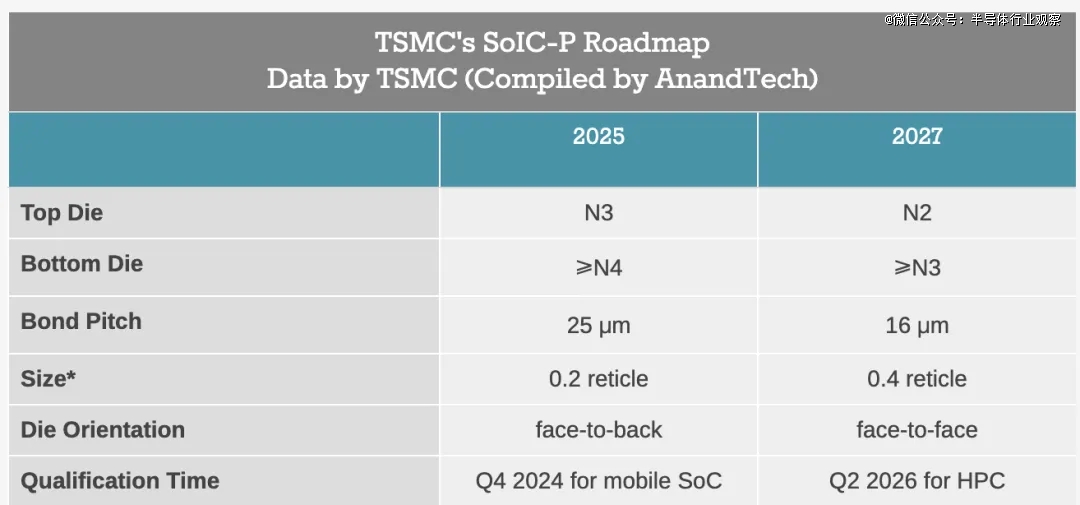

此外,除了针对需要极高性能的设备开发无凸块SoIC-X封装技术外,台积电还将在不久的将来推出凸块SoIC-P封装工艺。SoIC-P专为更便宜的低性能应用而设计,这些应用仍需要3D堆叠,但不需要无凸块铜对铜TSV连接带来的额外性能和复杂性。这种封装技术将使更广泛的公司能够利用SoIC,虽然台积电不能代表其客户的计划,但更便宜的技术版本可能会使其适用于更注重成本的消费者应用。

根据台积电目前的计划,2025年将提供正面对背面 (F2B) 凸块SoIC-P技术,该技术能够将0.2光罩大小的N3(3纳米级)顶部芯片与N4(4纳米级)底部芯片配对,并使用25μm间距微凸块 (µbump) 进行连接。2027年,台积电将推出正面对背面(F2F)凸块SoIC-P技术,该技术能够将N2顶部芯片放置在间距为16μm的N3底部芯片上。

为了让SoIC在芯片开发商中更受欢迎、更容易获得,还有很多工作要做,包括继续改进其芯片到芯片接口。但台积电似乎对行业采用SoIC非常乐观,预计到2026-2027年将发布约30种SoIC设计。

台积电强调,3D IC是将AI芯片存储器与逻辑芯片集成的关键方法。预估2030年全球半导体市场将成为万亿产业,其中HPC与AI为关键驱动力,占比达40%,这也让AI芯片成为3D IC封装的关键驱动力。

03 光电封装,台积电的下一个目标

在大力发展传统电封装的时候,光也成为了台积电的关注点。

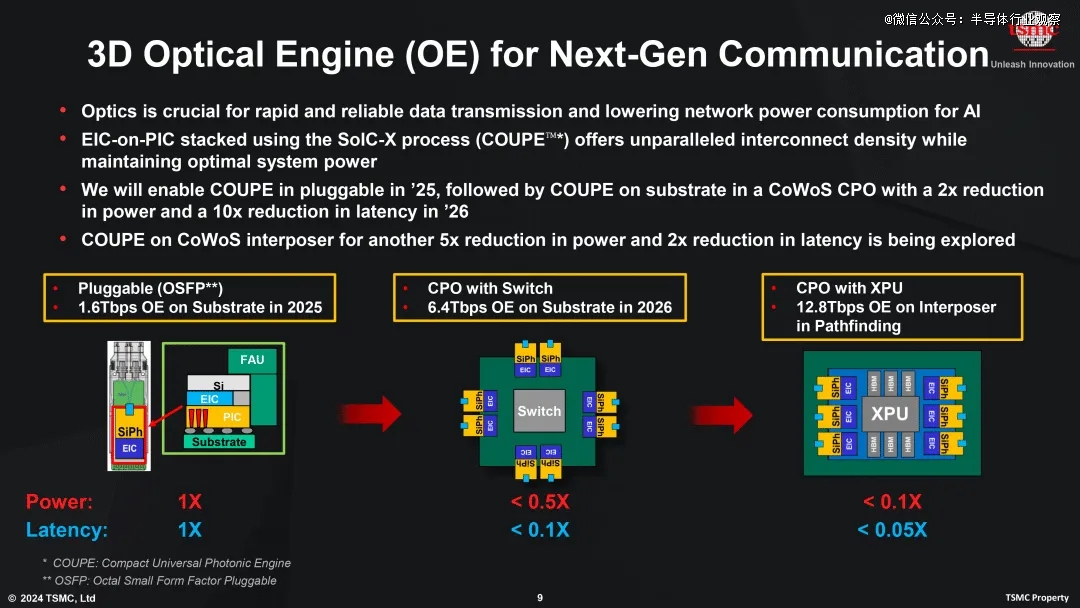

在今年的技术研讨会上,台积电还透露了“3D Optical Engine”战略,旨在将闪电般快速的光学互连集成到其客户设计中。随着带宽需求的激增,铜线逐渐无法满足前沿数据中心和HPC工作负载的需求,利用集成硅光子学的光学链路可提供更高的吞吐量和更低的功耗。

据了解,台积电正在开发紧凑型通用光子引擎 (COUP) 技术,以支持AI热潮带来的数据传输爆炸式增长。COUPE使用SoIC-X芯片堆叠技术将电子芯片堆叠在光子芯片之上,从而在芯片间接口处提供*阻抗,并且比传统堆叠方法具有更高的能效。

台积电计划在2025年使COUPE获得小型可插拔器件的认证,随后在2026年将其作为共封装光学器件(CPO)集成到CoWoS封装中,将光学连接直接引入封装中。

从其路线规划图中能看到,台积电*代产品以1.6Tbps的速度插入标准光纤端口,是目前高端以太网的两倍;第二代产品通过将COUPE与处理器一起集成到台积电的CoWoS封装中,将速度提升至6.4Tbps;路线图的最终成果是CoWoS“COUPE中介层”设计,其光纤带宽达到惊人的12.8Tbps。

目前,光学元件、硅光子元件还在比较初期的百花齐放阶段,随着AI时代需要的巨量运算、数据传输大量需求,耗能成为重要议题,硅光子元件的导入成为数据中心重要趋势。

此外,台积电还正在推进扇出式面板级封装(FOPLP)工艺,目前已经成立了专门的研发团队和生产线,只是目前仍处于起步阶段,相关成果可能会在3年内问世。魏哲家还表示未来英伟达和AMD等HPC客户可能会采用下一代先进封装技术,用玻璃基板取代现有材料。

总的来看,台积电正在加码进军先进封测领域,其中一个关键原因在于希望能延伸自己的先进制程技术,通过制造高阶CPU、GPU、FPGA芯片,并提供相应的封测流程,提供完整的“制造+封测”解决方案。

正如台积电董事长兼总裁魏哲家提出的“晶圆代工2.0”概念,即不仅包括传统的晶圆制造,还涵盖了封装、测试、光罩制作等环节,以及IDM(不包括存储芯片)。晶圆代工的界线逐渐模糊,因此扩大了定义。但台积电将专注于*进后段封测技术,以帮助客户制造前瞻性产品。

04 先进封装产能供不应求,台积电加速扩产

随着AI需求全面引爆,台积电CoWoS产能自2023年起面临持续紧缺。台积电总裁魏哲家今年7月表示CoWoS需求“非常强劲”,为应对强劲的客户需求,台积电正火速扩充先进封装产能。台积电将在2024年和2025年均实现产能至少翻倍,目标是在2025至2026年间实现供需的基本平衡,并计划在未来几年内继续加大投入,以确保产能的进一步扩充来满足市场需求。

业界预计,今年底台积电CoWoS月产能上看4.5万~5万片,较2023年的1.5万片呈现倍数增长,2025年底CoWoS月产能更将攀上5万片新高峰。

目前台积电共有五座先进封测厂,分别位于竹科、中科、南科、龙潭与竹南。其中竹南的AP6于2023年6月正式启用,为台积电首座实现3D Fabric整合前段至后段制程以及测试的全自动化工厂,经过了一年的运营,已成为中国台湾*的CoWoS封装基地。

这一扩产计划不仅体现在产能的翻倍上,还涉及多个新工厂的投入使用。2023年8月,台积电斥资171.4亿新台币购买了群创南科4厂(AP8厂区),预计明年下半年投产。该厂房预计未来的封装产能将是台积电竹南先进封装厂的9倍,供应链认为未来先进制程的晶圆代工、扇出型封装以及3D IC等产线都有可能会进驻。台积电此次收购群创南科4厂,主要是为了避免冗长的环评步骤,预计只需进行厂内改装,便可于明年正式投入生产。

除此之外,台积电还在嘉义科学园区建设2座CoWoS先进封装厂,规划中的两座封装厂预计在2028年开始量产,主要以系统整合单芯片(SoIC)为主。

值得一提的是,台积电不仅在台湾扩产,还在全球范围内寻找合适的建厂地点,甚至考虑在日本和美国建设先进封装厂。

近日有消息披露,台积电和芯片封装公司Amkor宣布,两家公司已签署了一份谅解备忘录,将在美国亚利桑那州合作进行芯片生产、封装和测试。台积电将利用这些服务来支持其客户,特别是那些使用台积电在凤凰城先进晶圆制造设施的客户。

此外,台积电还将与委外OSAT持续合作布局先进封装,以满足客户需求。

与此同时,CoWoS并不是台积电希望快速扩大产能的*先进封装技术生产线。该公司还拥有集成芯片系统 (SoIC) 3D堆叠技术,该技术的采用率有望在未来几年内不断增长。为了满足对其 SoIC 封装方法的需求,台积电将在2026年底之前以100%的复合年增长率扩大SoIC产能。

该产能计划从2023年底的约2000片月产能,在2024年底跃升至4000-5000片,并有望在2025年突破8000片,2026年再翻倍。由于大厂全数包下产能,台积电相关产能利用率将维持高档水平。

目前台积电SoIC技术已在竹南六厂(AP6)进入量产阶段,台积电还规划在嘉义先进封测七厂(AP7)分阶段扩建,不仅包括CoWoS技术,也涵盖SoIC。

上述一系列举动背后,体现出台积电积极应对市场需求的决心和策略。

从市场角度来看,台积电的新动作预示着它在全球半导体产业链中的重要性。随着技术的不断演进,竞争对手如三星、英特尔等也在加大对先进封装技术的投资。这使得台积电必须不断创新,以保持市场的*地位。通过对新工厂的布局,台积电可以快速提高市场份额,特别是在当前对高性能芯片需求激增的趋势下。

05 台积电的两把“利剑”

后摩尔时代,先进封装获重视,芯片封装测试随着半导体产业发展重要性日渐提升。

Yole强调,先进封装供应链正在经历显著转型。OSAT正在扩大其测试能力,而纯测试公司正在投资封装和组装。代工厂正在进入封装领域,对传统OSAT构成竞争威胁。来自不同背景的参与者正在进入市场。

不同商业模式的企业都在同一个高端封装市场空间展开竞争。但是不同业态的厂商,在封装业务方面投入的资源也有所不同,技术发展路线也存在差异。

针对代工厂来讲,由于2.5D/3D封装技术中涉及前道工序的延续,晶圆代工厂对前道制程非常了解,对整体布线的架构有更深刻的理解,走的是芯片制造+封装高度融合的路线。因此,在高密度的先进封装方面,Foundry比传统OSAT厂更具优势。

回顾台积电的迅速布局与目标,台积电的集成商业模式,结合前端制造与先进封装能力,正在成为行业的基准,将直接影响未来的市场格局。

ALETHEIA估计,台积电2026年来自封装事业的营收将会达到惊人的250亿美元,不只比2023年成长3.5~4倍,更超越所有成熟制程的总和,并与4、5纳米制程规模旗鼓相当,届时将贡献全年营收近2成比重。若进一步将台积电针对先进制程与CoWoS涨价考虑进来,台积电2026年营收上看1400亿美元,足足是2023年的2倍,获利部分更是2023年的近2.5倍。

再就半导体晶圆代工产业来看,目前完全没看到AI减速的迹象,反而在2/3/5纳米制程昂扬趋势与CoWoS扩产带动下,对台积电后市依然乐观。

正如文章开头所言:“台积电不仅是先进制程领头羊,先进封装明年也将起飞,有望成为*封装服务供应商,堪称半导体产业*的存在。”