据Kedglobal报道,全球*的存储芯片制造商三星电子公司将于本月晚些时候开始批量生产 290 层第九代垂直 (V9) NAND 芯片,以引领行业向高堆叠高密度闪存过渡的竞争对手。业内消息人士周四表示,随着人工智能时代对高性能和大型存储设备的需求增长,这家韩国芯片制造商还计划明年推出 430 层 NAND 芯片。

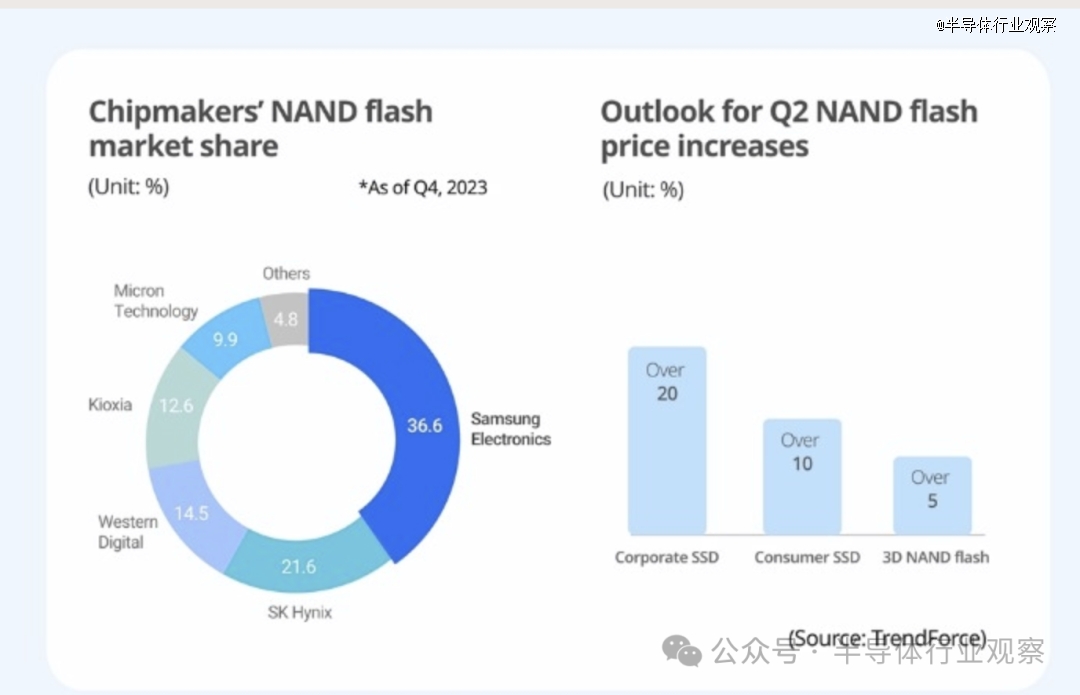

NAND 闪存是一种非易失性存储芯片,即使断电也能存储数据。它用于智能手机、USB 驱动器和服务器等设备。据市场研究公司 Omdia 预计,NAND 闪存市场在 2023 年下降 37.7% 后,预计今年将增长 38.1%。为了在快速增长的市场中占据一席之地,三星誓言要大力投资 NAND 业务。

自 2002 年以来,三星一直是 NAND 市场的*。

过去几年,各大芯片制造商都在进行一场“胆小鬼游戏”,以期在开发先进芯片堆叠技术以降低成本和提高性能的竞赛中击败竞争对手。随着人工智能芯片专注于推理,基于 NAND 的存储设备的竞争变得越来越激烈,这需要大容量的存储设备来存储和处理图像和视频。

更高密度的 NAND 芯片将加速数据密集型环境和工作负载,例如人工智能引擎和大数据分析。对于 5G 智能手机,增强的容量可以实现多个应用程序的更快启动和切换,从而创造更灵敏的移动体验和更快的多任务处理。

作为领头羊的三星,当然不会安于现状。

今年290层,明年430层

据报道,V9 NAND是继三星当前旗舰236层V8闪存产品后的一款尖端产品,面向大型企业服务器以及人工智能和云设备。消息人士称,V9 NAND 的重要之处在于三星利用了其双栈(double-stack)技术。

由于技术限制,三层堆叠(triple-stack )或三层单元(triple-level cell )技术被广泛认为是制造约 300 层芯片的最常用方法。据市场研究公司TechInsights Inc.称,三星预计将于明年下半年推出430层第10代NAND芯片。消息人士称,三星预计将采用三重堆栈技术来制造V10 NAND闪存。

三星电子一直致力于以最少的堆叠数量来堆叠最多的层数。SK海力士和美光科技公司应用了72层的双堆栈技术,而三星电子则采用了高达128层的单堆栈技术

三星高管曾多次表示,该公司的目标是到 2030 年开发超过 1,000 层的 NAND 芯片,以实现更高的密度和存储能力。

《首尔经济日报》在去年八月曾报道称,三星将拥有 300 层以上的 V-NAND(V 代表垂直或 3D NAND)芯片,准备于 2024 年投入生产,因此可能比 SK 海力士*一年之多,具体时间取决于三星多久能交付。当时三星最前沿的堆叠式NAND是236层产品,比美光和长江存储多了四层,但比SK海力士少了两层。

报道进一步指出,与SK海力士将采用三层堆栈的方式不一样,三星显然会坚持两层堆栈,这意味着三星的目标是每个堆栈超过150层NAND,就良率而言,这似乎是一个很大的风险。堆叠越高,堆叠失败的可能性就越大,但也许三星已经找到了围绕这一潜在问题的解决方案。

由于现代 3D NAND 依赖于硅通孔,因此与过去使用引线键合技术相比,更容易制造更密集的堆叠。但即便如此,这对于三星来说似乎也是一个很大的风险。如上所说,三星的路线图要求到 2030 年推出 1000 层以上的 V-NAND 产品,但这条路似乎仍然漫长而复杂。

其他巨头的堆叠技术混战

如上所述,除了三星以外,其他NAND巨头也都加入了堆叠层数竞赛。

首先看SK海力士方面,据报道,这家全球第二大内存芯片制造商公司计划明年初开始使用其三堆栈技术生产 321 层 NAND 产品。

去年8月,该公司在加利福尼亚州圣克拉拉举行的闪存峰会上展示了321层四维(4D)NAND样品。SK 海力士表示将于 2025 年上半年开始量产 1 太比特 (Tb) 三层单元 (TLC) 4D NAND 闪存。该公司表示,与 238 层、512 Gb 4D NAND 芯片相比,321 层 NAND 的生产率提高了 59%。

SK Hynix 使用 1 Tb 3D TLC 器件展示其 321 层 3D NAND 工艺技术的实力可能是一个好兆头,该公司打算在此节点上构建高容量 3D 器件。与现有工艺节点相比,这种潜力意味着每比特成本降低。这为更高容量 SSD 和其他基于 3D NAND 闪存的存储设备奠定了基础。

SK 海力士 NAND 开发主管 Jungdal Choi 在去年的一场演讲中表示:“凭借解决堆叠限制的另一项突破,SK 海力士将开启 300 层以上 NAND 时代并引领市场。”“随着高性能、大容量NAND的适时推出,我们将努力满足AI时代的要求,持续引领创新 ”Chi继续说。

关于未来的NAND规划,SK海力士最近两年很少详谈,但在2021年的一个分享中, SK 海力士表示,公司相信通过将层数增加到 600 层以上,可以继续提高 3D NAND 芯片的容量。但是,通过增加层数,SK Hynix(以及其他 3D NAND 生产商)将不得不继续使层更薄、NAND 单元更小,并引入新的介电材料来保持均匀的电荷,从而保持可靠性。该公司已经跻身原子层沉积领域的*之列,因此其下一个目标之一是实施高深宽比 (A/R) 接触 (HARC) 蚀刻技术。此外,对于 600 多个层,它可能必须学习如何串堆叠多个晶圆。

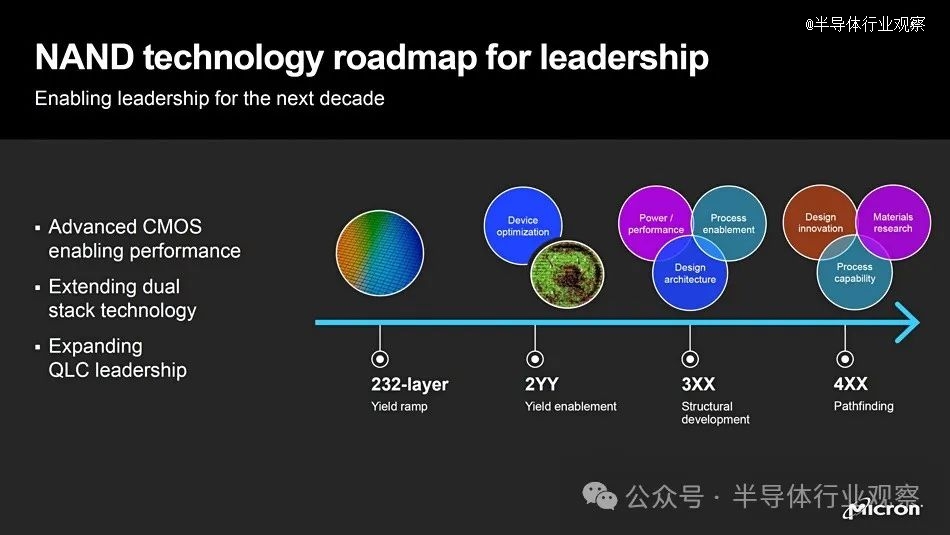

再看美光,根据之前的报道,美光已经制定了发展到 500 多层的路线图。

如图所示,美光也是双堆栈技术的支持者,具体而言,该技术是指将两个 3D NAND 芯片逐层堆叠,即所谓的“串堆叠”。这克服了半导体制造困难,例如随着层数增加而蚀刻穿过层的连接孔。随着孔深度加深,此类孔的侧面可能会变形,从而妨碍 NAND 单元正常运行。

美光表示,它的重点是 QLC(4bits/cell)NAND,但没有提及通过PLC(五级单元)将单元位数增加到 5 个,西部数据正在研究 PLC,Soldigm 正在开发 PLC。我们认为这是因为美光公司持谨慎态度,而不是因为它认为 PLC NAND 不可行而拒绝它。

铠侠则在早前的报道中披露了1000层的信息。据Xtech Nikkei报道,Kioxia 首席技术官 (CTO) Hidefumi Miyajima 表示,该公司计划到 2031 年批量生产超过 1,000 层的 3D NAND 存储器。

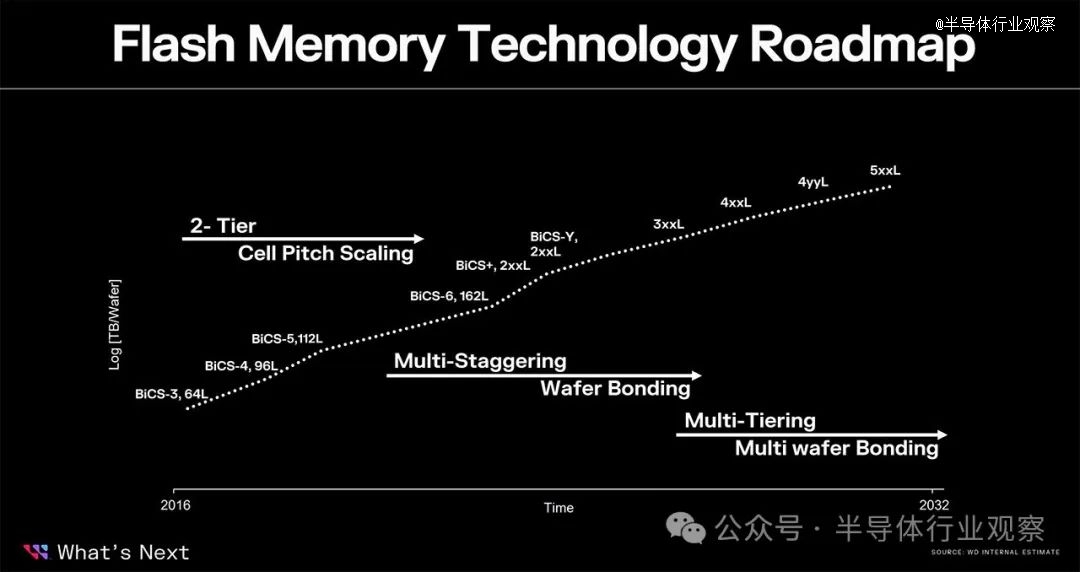

如今,Kioxia *的 3D NAND 器件是第八代 BiCS 3D NAND 存储器, 具有 218 个有源层和 3.2 GT/s 接口(于 2023 年 3 月首次推出)。这一代引入了一种新颖的CBA(CMOS直接键合到阵列)架构,该架构涉及使用最合适的工艺技术单独制造3D NAND单元阵列晶圆和I/O CMOS晶圆并将它们键合在一起。其结果是产品具有增强的位密度和改进的 NAND I/O 速度,这确保了内存可用于构建*的 SSD。

与此同时,Kioxia 及其制造合作伙伴 Western Digital 尚未披露 CBA 架构的具体细节,例如 I/O CMOS 晶圆是否包括额外的 NAND 外围电路(如页缓冲器、读出放大器和电荷泵)。通过分别生产存储单元和外围电路,制造商可以为每个组件利用最高效的工艺技术,随着行业向串堆叠等方法发展,制造商将获得更多优势,串堆叠(string stacking)肯定会用于 1,000 层 3D NAND。

3D NAND 技术路线图

对于NAND未来如何发展,如上所述,不同厂商又不同的方案。今年三月,业内知名机构techinsights从他们的角度,分享了3D NAND 技术路线图。

Techinsights表示,三星将 V7 的单层结构改为双层结构,并将 2D 阵列外围设计改为单元外围 (COP:cell-on-periphery) 集成。三星已经向市场发布了V8 236L 1 Tb TLC产品,这是他们的第二个COP结构。

去年,我评论说他们可能会多一个 300L 以下的节点,例如 n+1 的 280 或 290 层产品。因此,三星现在拥有 280L V9 COP V-NAND。此外,三星还在128L V6中添加了适用于990 EVO的133L V6 Prime版本,即所谓的V6P。133L是没有COP结构的单甲板(single deck )。总门数为 133 个,有效字线数从 128 个增加到 133 个,速度增加到 1600 MT/s,512 Gb 芯片上有两个平面,每个平面有两个子平面。下一代V10将采用类似于KIOXIA 218L CBA和YMC Xtacking产品的混合键合技术。

KIOXIA和WDC保持BiCS结构,市场上的大部分产品仍然是第五代112L。去年,我们终于采购了162L BiCS第六版。BiCS6 162L 可能是一个有风险的产品,并且可能不会持续很长时间。铠侠已经宣布他们将跳过 BiCS 第七代,相反,即将推出的 BiCS 第八代将有 218 层,而正在开发的下一款将有 284 层。218L和284L都将采用两片晶圆的混合键合技术,如果3xx层开发进展顺利,284L可能会再次跳过。

美光将 128L 的 FG CuA 集成更改为 CTF CuA 集成,此后,他们*于其他竞争对手向市场推出了 176L 和 232L 产品。美光正在开发 Gen7,这是一个2XX层的产品, 比300L 低,和三星280L类似。美光可能会在没有 300 层器件的情况下进军 400 层器件。我们知道Solidigm 144L QLC NAND由三层组成,这意味着三重48L结构。下一代 192L QLC 器件已于去年发布并进行了分析。然后下一个将是230L的分层QLC;然而,由于SK海力士指导的NAND业务计划不确定,他们的计划可能会改变。

SK海力士延续了4D PUC结构。2024年SK海力士V7 176L继续,238L V8 4D PUC量产产品很快将在市场上广泛应用。它去年已经发布了 321 层 V9 4D PUC 样品,下一个可能会有另外 3yy 层,例如 400 层以下的 370 或 380 层左右。

MXIC已向市场提供*代3D NAND芯片,例如用于Nintendo Switch的48L 3D NAND芯片。我们现在正在采购零件。MXIC正在开发第二代96L。

两三年后,我们或许就能看到超过500层的3D NAND产品,甚至五年后就能看到超过600层或700层的封装解决方案,采用更先进和优化的混合键合技术。