👆如果您希望可以时常见面,欢迎标星🌟收藏哦~

最近,内存专家Jim Handy发表了一篇有关 Compute Express Link (CXL) 的博客,以及他认为有关该技术的两个难题。

CXL 是一种基于开放标准的相对较新的缓存一致性内存协议,旨在使大型内存池可供大型计算机系统和数据中心中的多个处理器使用。在我看来,CXL 的中心目标是帮助数据中心架构师避免过度配置多处理器系统中的每个 CPU 或带有 DRAM 的大型数据中心中的服务器。

当您不知道系统中的 CPU 将负责执行什么类型的工作负载时,就会出现这种过度配置的问题,因此您需要为最坏的情况配置 DRAM。如果 CPU 能够以某种方式逐个任务地从中央池中获取一块内存,那么这些 CPU 就不需要过度配置自己的内存。他们可以根据需要请求内存。

为了实现这一壮举,CXL 内存需要比本地内存更松散地与 CPU 耦合。CPU 几年前吸收了 DRAM 控制器,以消除与本地 DRAM 外部内存控制器相关的延迟和功耗。如今,CPU 的三个关键品质因数是其拥有的片上 DRAM 控制器的数量、这些控制器可以命令的 DRAM 类型以及片上内存控制器与附加设备之间的 DRAM 事务处理速度。DRAM 以兆传输/秒 (MT/sec) 或千兆传输/秒 (GT/sec) 为单位。所有这些因素共同决定了您可以将多少本地内存连接到 CPU 以及该内存的执行速度。CXL 通过消除片上内存控制器,极大地扩展了 CPU 可以访问的内存量。

CXL 1.0 于 2019 年出现,CXL 联盟于 2022 年 8 月宣布了 CXL 3.0 规范。CXL 协议在 PCIe 的 I/O 语义之上添加了一致性和内存语义。CXL 3.0 通过采用 PCIe 6.0,将该协议的*传输速率提高了一倍,达到 64 GT/s。由于它基于 PCIe,业界发现 CXL 规范的物理部分易于理解和使用。

特殊的 CXL 交换机与 PCIe 交换机类似,基于 CXL 专用内存控制器将多个 CPU 与多个 CXL 内存子系统连接起来。CXL 交换机允许以编程方式设置和拆卸许多有趣的 CPU/内存系统拓扑。CXL 还使得将内存中保存的大数据块从一个 CPU 传输到另一个 CPU 变得更加容易和快捷。传输任意大小的数据块只需将指向该数据的地址指针从一个 CPU 传递到另一个 CPU。CXL 实质上将大型系统或整个数据中心中的所有可寻址内存组合成一个大型内存池,可供系统中的每个 CPU 访问。

以下是Jim Handy 的博客原文:

CXL 的神奇之处主要在于它可以向系统添加内存,而不会因大量电容负载而使处理器陷入困境,也不会因添加内存通道而消耗大量电量。它通过允许 CPU 通过高度简化的 PCIe 通道与由其自己的控制器管理的 DRAM 进行通信来实现这一点。

通过添加 CXL 交换机,多个处理器可以访问相同的内存,从而允许将内存分配给一个处理器或另一个处理器,就像灵活分配其他资源(如处理器和存储)一样。换句话说,CXL 分解了内存。

那么CXL面对的两个难题是:

1) CXL 的内存销量会增加还是减少?

这项新技术的好处之一是,CXL 连接的内存给 CPU 带来的电容负载很小,因为它位于 CXL 通道的另一端,这是点对点连接。CXL DRAM 模块具有一个控制器,该控制器一侧与 CXL 通道通信,另一侧与 DRAM 通信。如果单个 CXL 模块包含大量 DRAM 芯片,则该控制器的任务是驱动所有这些芯片及其所有电容负载,而处理器不必担心它。

DRAM 制造商认为这是一个潜在的福音,因为围绕 CXL 构建的系统可以支持比直接连接到处理器更大的内存量。美光 2023 年 3 月的白皮书:美光关于 CXL 对 DRAM 位增长率影响的观点表示:“CXL 将有助于维持比没有它时更高的 DRAM 位增长率。” 虽然这是一个相对温和的说法,但在与美光及其竞争对手三星和 SK 海力士的对话中,他们将 CXL 描述为 DRAM 销售的火箭助推器,可能导致行业千兆字节增长曲线拐点。

但对 CXL 最感兴趣的最终用户是超大规模数据中心,他们有不同的观点。2022 年 10 月,微软和谷歌发表了一篇研究论文,标题为:Pond: CXL-Based Memory Pooling Systems for Cloud Platforms。该论文称:“我们的分析表明,通过跨越 16 个插槽的 Pond 池,我们可以将 DRAM 需求减少 7%,这对于大型云提供商来说相当于数亿美元。” 更详细的句子告诉我们:“我们的结果表明,池大小为 16 个插槽时,Pond 可以将所需 DRAM 量减少 7%,并假设 CXL 使延迟增加 222%。这意味着云服务器成本总体降低了 3.5%。”

我们怎样才能调和这两种相互冲突的观点呢?CXL 会增加还是减少 DRAM 销量?这是*个难题。

2) CXL 在内存/存储层次结构中处于什么位置?

这是记忆专家的第二个难题。它与 CXL DRAM 如何适应内存/存储层次结构有关:

它比 DRAM 慢,因为它位于控制器、最多两个交换机以及网络或通道后面;

它比 DRAM 更贵,因为它需要控制器;

CXL 模块类似于 DIMM,只不过 DRAM 和 CXL 通道之间有一个 CXL 控制器。该控制器增加了 DRAM 访问的延迟,同时也增加了模块的成本;

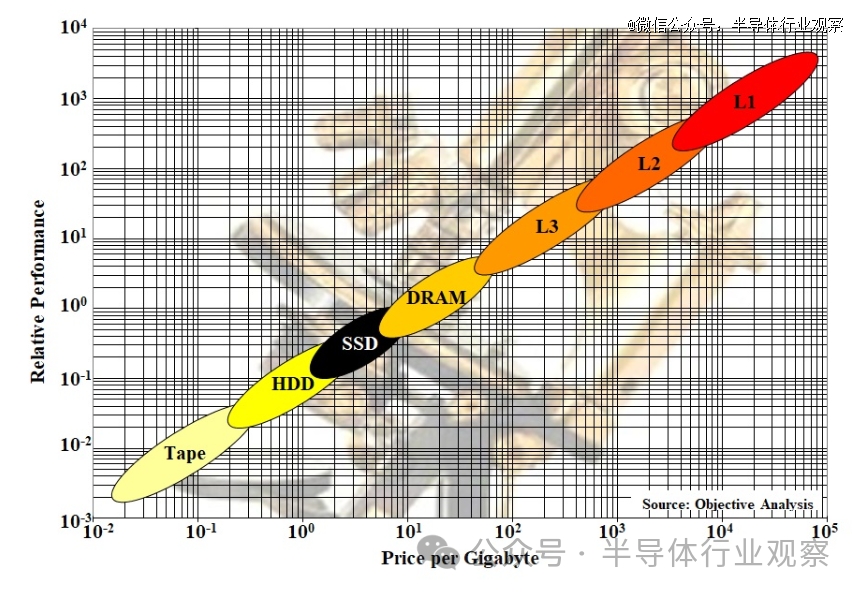

了解这一点重要性的一个好方法是查看我们在许多演示中展示的 Objective Analysis 内存/存储层次结构图。SSD Guy 的博客文章对此进行了详细描述,因此我仅在此展示而不解释:

内存或存储与其他技术位于同一对角线,适合此图表。任何新的东西都必须比下一个更快的层更便宜,并且比下一个更便宜的层更快。这些球体中的每一个都非常适合这张图表。

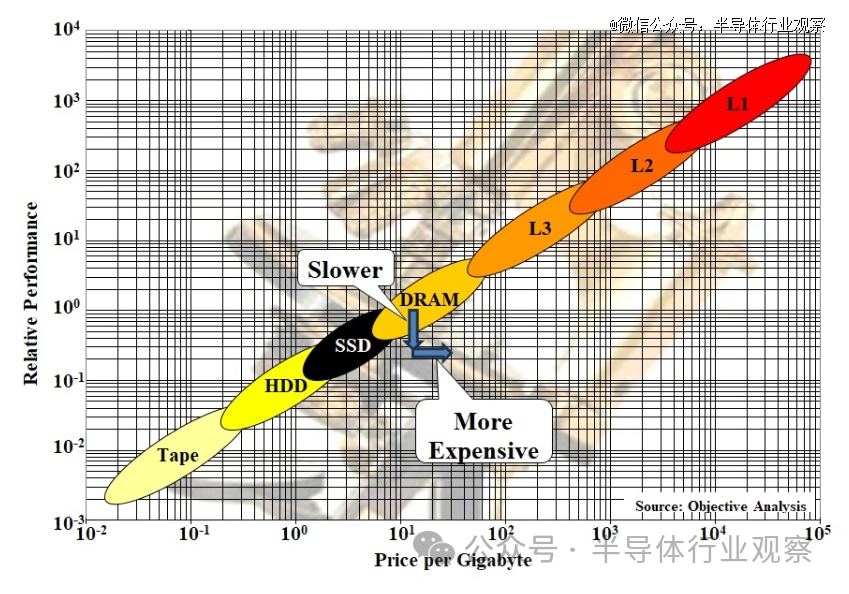

CXL 在哪里适合这个?由于近期主要针对 DRAM,因此它将减慢 DRAM 层的速度,同时增加其成本。这由下面的再现中的箭头表示:

简而言之,CXL 控制器后面的 DRAM 远离对角线,因此它不适合内存/存储层次结构。

精明的读者可能已经注意到,上面引用的 Pond 论文指出,CXL 为 DRAM 访问增加了 222% 的延迟,使其速度慢了三倍多。(诚然,这个数字来自测试设置,该设置很可能比明天基于 CXL 的系统慢。)尽管如此,CXL DRAM 模块的控制器确实给 CXL 连接的 DRAM 增加了大量的延迟。CXL 2.0 中定义的更复杂的系统通过将信号引导通过交换机而增加了更多延迟,增加了额外的延迟,而 CXL 3.0(如下)的结构支持通过将信号引导通过两个交换机来创建结构,从而导致更多的延迟。

但 CXL 连接的 DRAM 可以比直接连接的 DDR5 DRAM 具有更高的带宽,因为您可以将一大堆芯片放在控制器后面。CXL 支持者解释说,增加的带宽足以抵消增加的延迟。

在这里,我们遇到了决定哪个更重要的挑战:延迟或带宽。这一切都取决于主机上运行的应用程序。带宽匮乏的程序以及具有更可预测的数据访问模式的程序将受益于 CXL 的高带宽。数据访问模式更加随机的程序将受到 CXL 延迟的影响。

一些读者可能已经注意到,这个问题与几十年前硬盘世界中注意到的问题相同。在 20 世纪 80 年代,人们强烈主张串行数据访问速度与磁头延迟之间的关系。为了解决这个问题,设计了一种称为 IOPS 的新测量方法,它反映了典型应用程序的行为来测量两者的混合。也许记忆需要这样的衡量标准。

与此同时,基于 CXL 的 DRAM 的性能可能有利于某些应用程序,但会降低其他应用程序的性能。随着 CXL 得到更广泛的部署,这一点将变得更加明显。

从长远来看,CXL 允许非 DRAM 内存竞争该大容量设备。使用 DDR 的 CPU 上的直连通道对新技术非常不利,因为 DRAM 的详细状态机已融入通道操作中。任何不是 DRAM 的东西,都有不同的状态机,如果它试图竞争本地通道,就需要模仿外来的解决方案,这是一个巨大的障碍。新技术只是在实验室中停滞不前,无法投入商业应用。

然而,在 CXL 上没有人知道你是否是 DRAM。它是用于加载和存储操作的干净事务语义,以及有关一致性和隐私的补充信息。这创造了一个新的市场机会,不同形式的内存可以竞争相同的干净的加载-存储语义。这需要几年时间,但这才是 CXL.mem 可能带来的真正革命。更大、更低功耗、更密集且更便宜的主存储器。