最近,有专家呼吁业界尽早统一封测技术标准,特别是先进封装。

SEMI日本办事处总裁Jim Hamajima表示,芯片行业需要更多后端生产流程的国际标准,以使英特尔和台积电等晶圆厂能够更有效地提高产能。当前,台积电、英特尔等公司都在建设自家的先进芯片封装技术体系和生态系统,都在使用不同的标准,这样的话,生产效率并不高。

Jim Hamajima表示,包括芯片封装和测试在内的后端工艺比芯片制造的前端工艺(如光刻)更加“分裂”,而光刻等前端工艺广泛使用了SEMI制定的标准。他认为,随着公司追求更强大的芯片,这可能会影响行业的利润水平。

01 芯片制造门槛高,标准易统一

芯片制造是半导体产业门槛最高的板块,投资高、玩家少。目前,在先进制程芯片制造领域,仅剩下台积电、三星和英特尔这三家了。

芯片制造过程需要2000多道工序,可以分为8大步骤,包括:

光刻,它是通过曝光和显影程序,把光罩上的图形转换到光刻胶下面的晶圆上,光刻主要包含感光胶涂布、烘烤、光罩对准、曝光和显影等程序。曝光方式包括:紫外线、极紫外光、X射线、电子束等。

刻蚀,它是将材料使用化学反应或物理撞击作用而移除的技术,干法刻蚀(dry etching)利用等离子体撞击晶圆表面所产生的物理作用,或等离子体与晶圆表面原子间的化学反应,或者两者的复合作用,湿法刻蚀(wet etching)使用的是化学溶液,经过化学反应达到刻蚀的目的。

化学气相沉积(CVD)。

物理气相沉积(PVD)。

离子注入(Ion Implant)。

化学机械研磨(CMP)。

清洗。

晶圆切割(Die Saw)。

2000多道工艺流程中蕴藏着晶圆厂的智慧、核心技术和雄厚的财力,技术含量非常高,且需要长年的积累,并不是购买了先进的设备,就能造出合格的芯片。当然,先进的设备也很重要,巧妇难为无米之炊嘛。

由于投资巨大,技术含量非常高,特别是较为先进的制程工艺,企业进入的资金和技术门槛高,使得玩家比较少,而且,随着先进制程发展到3nm、2nm,门槛就更高了,且向前发展和演进的难度超高,仅有的几个玩家做起来也很吃力。在这种情况下,很难出现百花齐放的局面,统一标准就相对容易,且能使用较长时间。

02 封装测试新标准之争

封装测试是芯片生产的最后一环,多数情况下,封装测试的技术含量和实现难度比前端的芯片制造低。但芯片封装也是有标准的,这些标准相对较多,且变化也比前端的芯片制造标准快,特别是芯片正朝着高集成度、小特征尺寸和高I/O方向发展,对封装技术提出了更高要求,随着SiP及先进封装技术的出现和发展,需要重新定义芯片的封装和测试。与此同时,由于前端芯片制造面临技术和工艺发展瓶颈(如摩尔定律的失效),使后端封装成为晶圆大厂眼中的决胜关键,近年来,各大晶圆厂都在积极投资研发先进封装技术。

综上,前端芯片制造工艺难以突破,后端的封装又相对容易,这两大因素共同促使新封装技术和标准涌现。

全球范围内,先进封装的市场份额在2022年达到了47.2%,先进封装市场的增速超过了传统封装,预计到2026年,先进封装的市场份额将提升至50.2%。这种增长主要得益于AI和高性能计算领域的旺盛需求,这些领域对高集成度、高性能和低功耗芯片有着巨大的需求。

目前,先进封装技术仍然以倒装芯片(Flip-Chip)为主,3D堆叠和嵌入式基板封装(ED)的增长速度也非常快。此外,其它先进封装技术,如扇出型封装(Fan-Out)和晶圆级封装(WLCSP)也在市场上占据重要位置。这些封装技术在提高芯片性能和减少封装尺寸方面具有显著优势,广泛应用于智能手机和其它移动设备。

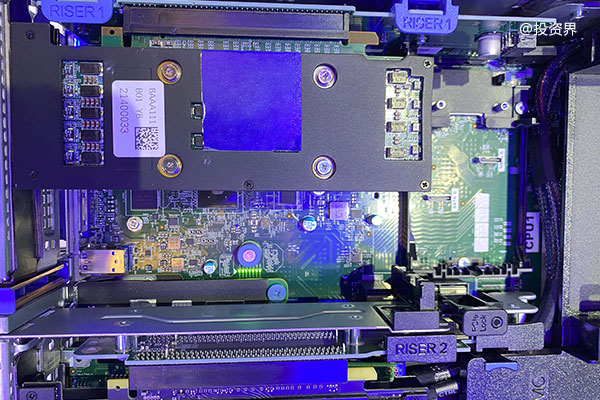

目前,先进封装应用最火的就是HBM内存。HBM通过逻辑芯片和多层DRAM堆叠来实现高速数据传输,每层之间通过硅通孔(TSV)和微凸点连接,突破了带宽瓶颈,成为Al训练芯片的*。HBM内部的DRAM堆叠属于3D封装,而HBM与其它部分合封于硅中介层,属于2.5D封装。

在高科技产业,一流企业制定标准,二流企业执行标准。半导体业是典型代表。

在先进芯片封装技术方面,大厂不仅遵守行业内的执行标准,还要超越这些标准,形成自己独特的标准和工艺,它们正在积极制定一系列规范和要求,包括工艺流程、设备参数、材料选择、质量控制等。这可以反映出芯片制造企业的技术水平和创新能力,有益于赢得客户、提升竞争力。

还有一点很重要,那就是与传统封装测试工艺不同,先进封装的关键工艺需要在前端芯片制造平台上完成,是前道工序的延伸。这显然是台积电、三星和英特尔等晶圆大厂的先天优势,因此,它们开发先进封装工艺就更加顺理成章了。

目前来看,在先进封装技术商业化方面,台积电起步早,市场影响力也*。

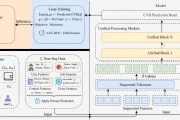

当下,火爆的HBM内存主要采用台积电的CoWoS封装技术。CoWoS是台积电于2012年研发的一种2.5D封装技术,可分为CoW(chip on wafer)和oS(on substrate)两步,CoW是将计算核心、I/O die、HBM等裸片封装在硅中介层上,然后再把CoW裸片整体封装在基板(Substrate)上,即oS环节。CoWoS可以节省空间,实现HBM所需的高互联密度和短距离连接;还能将不同制程的芯片封装在一起,在满足Al、GPU等加速运算的需求的同时控制成本。

据Omdia统计,,2023年第三季度,英伟达售出近50万个A100和H100芯片,得益于人工智能和高性能计算的需求,英伟达当季在数据中心硬件上获得了145亿美元的收入。除了英伟达,AMD的最新AI GPU产品MI300也要采用台积电的CoWoS(2.5D)和SolC(3D)封装技术。庞大的需求量导致CoWoS产能供不应求。

除了CoWoS,台积电还在开发新的封装技术,据报道,该晶圆代工龙头已经组建了专门的团队,切入专业封装测试厂(OSAT)过去多年来一直开发的FOPLP(Fan-out Panel Level Package)封装技术。台积电开发的FOPLP可以看作是矩形CoWoS封装,目前主要针对以英伟达为主的AI GPU领域,具有单位成本更低、封装尺寸更大等优势。未来还可以进一步整合台积电3D Fabric平台上的其它技术,为2.5D/3D先进封装解决方案服务于高端产品应用铺路。

看到台积电在先进封装市场搞得风生水起,三星和英特尔要加把劲儿了。

三星、英特尔也意识到了问题,纷纷投入新一代先进封装技术的开发工作。

目前,三星自研的先进封装技术和服务包含I-Cube(2.5D),以及X-Cube(3D)等。对于智能手机或可穿戴设备等需要低功耗内存的应用,三星已提供面板级扇出型封装和晶圆级扇出型封装平台。

三星的I-Cube封装技术有多个版本,其中,I-Cube S是一种异构技术,将一块逻辑芯片与一组HBM裸片水平放置在一个硅中介层上,可实现高算力、高带宽数据传输及低延迟,I-Cube E技术采用硅嵌入结构,拥有PLP(面板级封装技术)大尺寸、无硅通孔结构的RDL中介层等特点。H-Cube是一种混合载板结构,将ABF载板和 HDI(高密度互连)技术相结合,可在I-Cube 2.5D封装中实现较大封装尺寸。

英特尔正在推广其嵌入式多芯片互连桥(EMIB)2.5D封装技术。结构简单、信号干扰低是EMIB的主要优势,应用这一技术,封装过程中无需制造覆盖整个芯片的硅中介层,以及遍布在硅中介层上的大量硅通孔,使用较小的硅桥在裸片间进行互联即可。与普通封装技术相比,EMIB由芯片I/O至封装引脚连接并未发生变化,无需再通过硅通孔或硅中介层进行走线。这种架构和工艺,不仅可以降低不同裸片间的传输延时,还减少了信号传输干扰。

由于三星和英特尔的先进制程(5nm以下)市场影响力和商业化水平明显弱于台积电,在这种情况下,对前端芯片制造工艺和平台依赖度很高的先进封装技术,就很难打开局面,赚钱能力有限。

由于先进封装的市占率越来越大,晶圆厂又有先天发展优势,这就使传统OSAT封测厂有些尴尬,发展脚步不如台积电那么顺畅。台积电在先进封装领域的强势地位,促使其将更多资源投向先进封装技术和服务,以进一步巩固市场地位。这可能会使OSAT企业的机会越来越少。

日月光投控、安靠科技等传统OSAT大厂并不会坐以待毙。

就广义上的先进封装而言,传统OSAT依然占据着较大的市场份额,据Yole统计,2022年,先进封装市场,OSAT的市场份额为65.1%,IDM的市场份额为22.6%,晶圆代工厂的市场份额为12.3%。其中,日月光占比最高,达到25.0%,安靠占比12.4%,台积电占比12.3%,三星占比9.4%,英特尔占比6.7%。然而,IDM和晶圆代工厂主攻高端3D封装,而OSAT普遍较为传统,主攻中低端倒装、晶圆级封装,这在AI用处理器和HBM内存快速发展的当下,发展的势在IDM和晶圆代工厂一边,要想赶上发展潮流,OSAT封测厂必须将更多资源投向高端封装工艺和服务。

以封测龙头企业日月光为例,正在开发新的封装技术,如扇出型基板上晶圆封裝(FOCoS)。FOCoS是一种安装在高引脚数球栅阵列 (BGA) 基板上的扇出封装倒装芯片技术,扇出封装具有重新分布层(RDL),允许在多个芯片之间构建更短芯片到芯片 (D2D) 互连,倒装芯片安装到BGA基板上。FOCoS-CF由两个面朝下的ASIC小芯片组成,通过Cu通孔直接与RDL连接,硅裸片和扇出RDL之间没有微凸块。FOCoS-CL中,ASIC裸片和两个HBM通过RDL和Cu微凸块连接。FOCoS-Bridge使用硅桥芯片嵌入扇出RDL层连通ASIC和HBM。

为了赶上先进封装热潮,日月光投控财务长董宏思指出,面对当前市场的需求,将增加2024年的资本支出,在2023年15亿美元的基础上提高一倍。其中,封装支出占比约53%,测试支出占比约38%。先进封装是投资重点。

03 中国大陆封测厂加紧跟上

在先进封装发展如火如荼的当下,中国大陆相关企业也在开发相关技术,争取跟上产业发展脚步。

长电科技是中国大陆封装行业的领军企业,该公司正在开发XDFOI技术(2.5D超高密扇出型封装)。该封装技术可以将不同功能的裸片整合在系统封装内,特别适用于对集成度和算力要求较高的应用,如FPGA、CPU、GPU和5G网络芯片。XDFOI技术不仅可以提高集成度,还可以提升性能和功率效率。

通富微电的VISionS技术能够实现多层布线,将不同工艺和功能的Chiplet小芯片高密度集成,提供晶圆级和基板级封装解决方案。该公司已经实现了堆叠NAND Flash和LPDDR封装的量产,其3D存储封装技术处于国内*水平。

华天科技推出了3D Matrix技术,集成了硅通孔、eSiFo(Fan-out)和3D SIP等先进封装技术,Fan-out技术通过在基板上刻蚀挖槽,将芯片放置在凹槽内,再进行重新布线和封装,显著提高了封装密度和性能。

此外,华为、比亚迪半导体、阿里巴巴等产业链多个环节上的企业,在封装设计、应用和市场推广等方面发挥着重要作用。