最近,先进半导体工艺制程方面的消息有不少。就在过去一周,相关的新闻包括:

联发科宣布率先完成3nm工艺的下一代SoC的开发,打破了苹果*使用下一代工艺制造手机SoC的惯例

Intel CEO预期将在2025年借助18A工艺来追上甚至超越TSMC和三星在先进制程领域的*位置,目前已经有大客户支付了大额预付款来使用该工艺

Intel预计将在未来两年内继续大量使用TSMC工艺来生产*进的处理器产品(Meteor Lake及后续产品),在未来两年Intel估计会使用超过150亿美元来使用TSMC的工艺

Intel和三星正在合作开发下一代内存-处理器堆叠产品(cache DRAM),该技术作为对AMD的3D V-Cache的回应,将DRAM直接堆叠在CPU上,从而大大提升系统的集成度和性能

三星在美国的4nm工厂预计在2024年底完成,超过TSMC在美国建厂的速度

从这些消息,我们可以看到的是,首先,随着以人工智能为主力的新需求渐渐推动半导体市场渐渐复苏,对于先进制程产能的需求非常旺盛,而晶圆制造厂对于扩大先进制程产能也抱着积极的态度。而在另一方面,全球范围内几大瞄准先进制程的巨头目前的竞争格局也很清楚:TSMC是先进制程领域的领跑者,其良率和性能都能*一步达到较高的水准,同时TSMC还拥有全球*的先进封装技术,因此凭借这样*的综合地位领跑整个先进制程市场,大客户纷纷在TSMC下单导致产能无法满足需求。

三星是先进工艺领域的有力竞争者,随着其技术成熟度与TSMC逐渐接近以及TSMC产能紧张,未来预计也会获得先进制程领域的大量订单。而Intel则是先进工艺领域的新进竞争者。Intel在最近才真正进入先进制程的竞争有两重原因:*是因为Intel之前在10nm工艺节点的开发中拖延了太久,导致其技术在过去几年中大大落后与TSMC和三星;但是随着Pat Gelsinger成为Intel CEO位置后进行大刀阔斧的改革,目前Intel在先进工艺技术领域与TSMC和三星的差距已经在快速缩小,预计在未来两年内有机会能真正和TSMC/三星同步推出最新工艺制程。第二个原因是Intel在Pat Gelsinger执掌CEO之后正式决定大规模投入晶圆代工领域,从而与TSMC和三星真正开始直接竞争(而在这之前Intel并不大规模开放自家工艺,因此和TSMC/三星并没有直接竞争关系)。

我们在先进半导体制程看到了乐观的市场预期和火热的竞争;但是,在竞争之外,几大晶圆制造厂之间也有合作关系,这就让这些公司之间的关系变成更加微妙的竞争-合作关系。例如,Intel目前最主要CPU业务线中,还必须依靠TSMC。在Intel的Meteor Lake中,预计GPU tile会使用TSMC的工艺,而CPU则使用Intel自己的工艺。另一方面,Intel也在和三星合作内存堆叠技术(cache DRAM)以追赶AMD在这方面的*地位。

先进封装带来的变化

过去20年间,芯片设计行业的主流设计范式是SoC。SoC设计方法给芯片行业带来了极大的繁荣,但是在先进制程时代,这样的设计方法会由于先进封装技术而发生改变,而这样的改变也会对先进制程晶圆制造厂的竞争合作关系带来改变。

在SoC设计方法中,SoC芯片由许多IP组成。芯片设计公司在设计SoC时,首先定义需要SoC上需要的IP,并且从第三方IP提供商处获取IP或者自己设计IP;然后把这些IP集成到芯片上,最后把整个SoC送到晶圆制造厂中进行流片制造。

在SoC设计方法中,芯片设计公司更多的是关注SoC系统以及每个IP的设计,但是在芯片制造的时候,所有的IP都会使用同样的工艺去制造,而不可能对于不同的IP使用不同的工艺去制造。

而随着先进工艺和先进封装的发展,这样的SoC设计方法正在慢慢被芯片粒(chiplet)设计方法取代。先进工艺的成本很高,良率却并不容易做高,为了提高良率,通常的方法是把大芯片分成多个芯片粒,并且使用高级封装技术做芯片粒之间的整合。目前,AMD、Intel等都已经在最新的处理器产品中使用这样的芯片粒设计,预计未来芯片粒设计将会成为更多使用先进制程的大型芯片的选择。

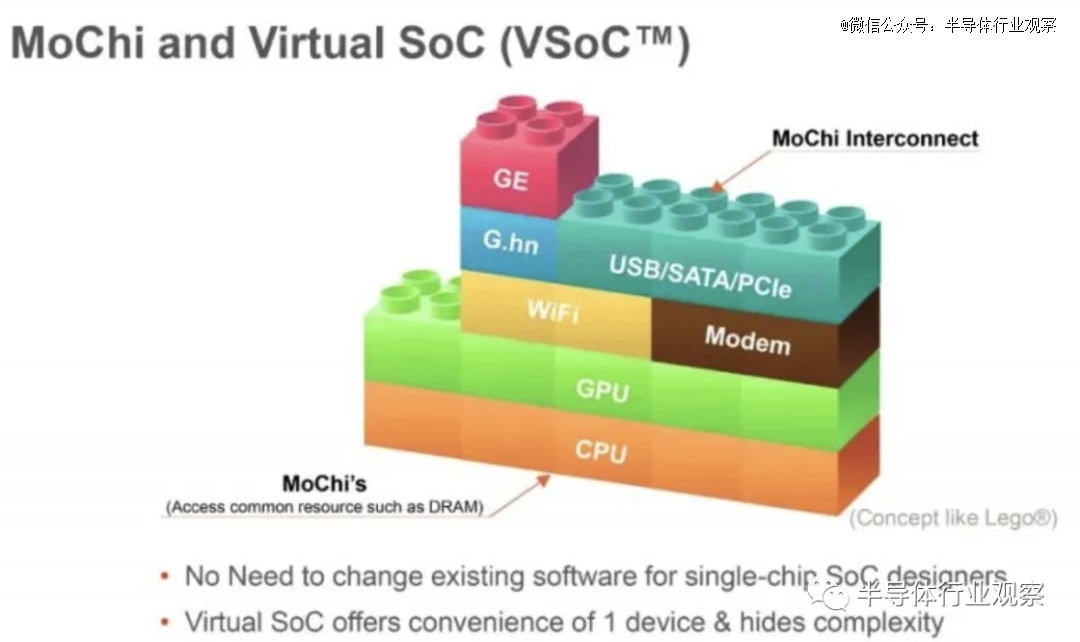

而一旦SoC设计方法慢慢被芯片粒设计方法所取代,SoC设计方法中“整个SoC都要使用相同半导体工艺制造”的假设也就不再成立,因此每一个芯片粒都可以使用不同的工艺来制造。正如2015年Marvell在ISSCC上提到的MoChi概念一样,整个基于芯片粒的设计把整个芯片系统拆分成了多个芯片粒,每个芯片粒都可以使用最适合的工艺来制造,并且最终整合在一起。

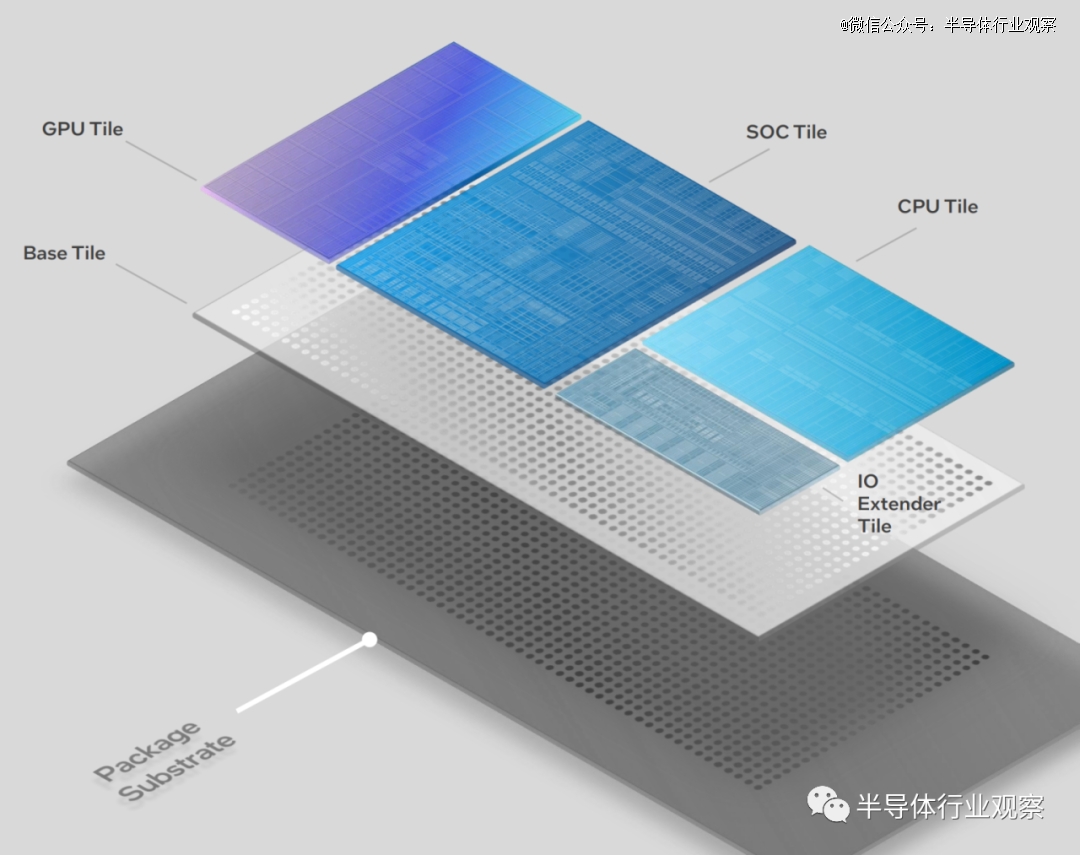

我们在Intel的Meteor Lake中就看到了这样的设计。在Meteor Lake中,分成了多个芯片粒(Intel称之为“tile”),包括CPU Tile,GPU Tile,SOC Tile和IO Tile等,这些不同的Tile都可以用不同的工艺制造并且最后使用高级封装技术集成在一起。在Meteor Lake中,CPU Tile使用Intel的工艺,而GPU Tile则会使用TSMC的工艺。

差异化将是未来演化方向

当使用先进工艺的芯片设计方法逐渐从SoC转向芯片粒,晶圆制造厂未来的订单也可望逐渐从整个SoC慢慢转向单独的芯片粒。芯片设计厂商可以选择最适合的晶圆制造厂去制造相应的芯片粒并且最后集成到一起。芯片粒设计方法加上先进工艺自身的特性,可能会让未来晶圆制造厂越来越专注于差异化。

先进制程很贵,但是带来的性能提升并不大。在九十年代摩尔定律的黄金时代,每次工艺节点缩小都可以实现晶体管性能几乎翻倍;而在目前,每一代工艺演进带来的晶体管性能提升仅仅在10-20%左右。可以想像,芯片设计公司在大成本投入先进工艺制造芯片后,也必然希望这样的高投入能获得尽可能大的回报,因此希望可以在芯片粒的颗粒度上实现每个芯片粒的性能*。

而在另一方面,由于先进工艺研发难度巨大,且研发成本投入巨大,因此不太可能出现一家晶圆制造厂在性能、功耗、成本等领域全方位大幅*其他晶圆制造厂的情况,更有可能是在不同的设计领域,不同的晶圆厂各有所长,从而实现差异化竞争。这里的差异化,既包括了在性能、功耗、成本等指标维度的区别;也包括了不同的厂商擅长不同领域的芯片粒,例如TSMC擅长高性能计算,三星擅长存储相关领域等。

在这样的情况下,不同晶圆厂差异化竞争,都各有自己擅长的方向,而芯片设计公司则各取所长,使用不同的晶圆制造厂去做最擅长领域的芯片粒并且最后整合在一起,可能就是未来的新竞争格局。Intel的Meteor Lake中,GPU Tile使用TSMC制造,就是因为TSMC擅长高性能计算芯片粒;而CPU Tile使用Intel的工艺制造,也是因为Intel在CPU领域的工艺-芯片协同设计有着几十年的积累。未来Meteor Lake这样的不同晶圆厂制造不同芯片粒可望会成为主流,而这也会让晶圆厂走差异化竞争的道路。

先进封装将是先进制程竞赛中的

核心竞争力

如前所述,芯片粒设计方法将大大改变晶圆制造厂在先进制程领域的竞争格局,而在上述分析中,不应忽视的是先进封装技术也将成为一个重要变量,因为先进制程芯片(尤其是高性能计算芯片)离不开先进封装技术。而且更关键的是,先进封装技术在未来将会和先进制程越来越紧密地结合,而掌握这些先进封装技术的也恰恰是TSMC、Intel和三星这样的先进制程晶圆制造厂,而不是第三方封测厂。

在未来,先进封装的重要性甚至不亚于先进制程的优化能力,未来的晶圆制造厂竞争力将会取决于半导体工艺和先进封装技术的综合。例如,目前TSMC能获得Nvidia H100 GPU订单的一个重要因素,就是因为TSMC同时拥有*进的4nm半导体制造工艺以及CoWoS先进封装技术,而目前H100供不应求事实上是被CoWoS产能所限制,而不是4nm半导体工艺产能所限制。事实上,由于先进封装和先进制程供货商互相重合,晶圆制造厂甚至有可能利用其在某一方面的优势来撬动市场(例如,利用其在先进封装领域的优势来弥补其在某个领域先进制程上的劣势来获得订单)。

展望未来,TSMC目前虽然同时拥有先进封装和先进工艺方面的*地位,但是Intel在EMIB等先进封装技术上已经有很久的技术积累,随着Intel在先进半导体工艺追赶,未来两者结合会有相当的竞争力;而Samsung的I-Cube/H-Cube和X-Cube等先进封装技术可望也会在SoC/内存集成领域有自己独特的优势。未来的先进工艺晶圆厂之间的竞争格局远未尘埃落定,值得我们关注。