最近来自数据中心三大厂商英特尔、英伟达和AMD三大半导体厂商的消息颇多,无论是AMD收购赛灵思,还是英特尔最近透露的Falcon Shores,再加上去年英伟达所推出的Grace CPU,CPU厂商开始研究GPU、GPU厂商开始研发CPU,这些动作无不是释放一个明显的信号,芯片行业正在向异构架构整合发展。而部分国内厂商也嗅到了这个先机,开始往多架构产品线布局。异构计算,要全面爆发了吗?

01 三大厂商引领异构计算

异构计算(英语:Heterogeneouscomputing),又称为异质运算,早在80年代中期就产生了,其主要是指使用不同类型指令集和体系架构的计算单元组成系统的计算方式。常见的计算单元类别包括CPU、GPU、DSP、ASIC、FPGA等。目前“CPU+GPU”以及“CPU+FPGA”都是受业界关注的异构计算平台。

现在随着5G、AI、云计算等新兴领域对计算量的需求,已经超过了通用CPU的发展速度,仅通过提升CPU时钟频率和内核数量而提高计算能力的传统方式遇到了散热和能耗瓶颈,所以需要GPU、FPGA、DSP,现在还多了DPU,这些计算单元去配合CPU进行并行计算,大家分工协作,“专人干专事”,以此来很好的满足这些计算需求。

而英特尔、AMD、英伟达三大厂商最近的一些列集中的动作更是把异构计算推上了风口浪尖:

英特尔CPU+GPU新架构Falcon Shores

英特尔在最近的投资者会议中提出了一个新架构——Falcon Shores。这是一款将X86和Xe GPU 整合到一个Xeon插槽中的新架构。该架构将利用英特尔埃米时代工艺技术、下一代封装、英特尔正在开发的新型超带宽共享内存以及*的I/O技术。他们预计,相对于当前平台,Falcon Shores将提供超过5倍的每瓦性能、超过5倍的计算密度增加以及超过5倍的内存容量和带宽提升。据路线图所示,Falcon Shores计划于2024年完成。

目前英特尔已经有CPU、FPGA、IPU等产品线,现在也投入了运算级GPU的研发,在Intel 投资日上,英特尔谈到了两款GPU产品,分别是面向游戏玩家的Xe-HPG架构Alchemist GPU以及面向数据中心的Xe-HPC架构GPU芯片Ponte Vecchio,后者是MCM(Multi-chip Module)/chiplet形态的GPU芯片。而且近日,AMD独立GPU等项目的首席SoC架构师Rohit Verma也从AMD跳槽到英特尔。英特尔这次GPU的动作可以说计划长远、且非常大。

英伟达Grace CPU

2021年4月,英伟达公布了其*代号为Grace的CPU产品,这是专为人工智能和超算使用需求打造的。该产品采用下一代Arm Neoverse内核,在NVIDIA放出的设计示图中,Grace CPU是以MCM(Multi-Chip Module,多芯片模组)形式构成,包括CPU、GPU、DPU和带有ECC的LPDDR5x的新型高带宽内存子系统,辅以使用 NVLink 通道技术。可以说是专为连接英伟达GPU所设计。据悉,Grace预计在2023年发布。

英伟达的Grace视图不是一个芯片,而是多模块形式(图源:英伟达)

对于英伟达来说,Grace CPU的研发将对其意义深远,使其不必完全受制于AMD和英特尔在CPU上的的合作关系,可以说是自立自强的一个表现。因为即使GPU的并行能力不断提高,但GPU终究在加速运算中扮演资料运算,仍需搭配CPU执行基本的系统,以及由CPU 发号运算的命令,所以GPU和CPU之间的沟通很重要。而x86架构的CPU又受限PCIe频宽的影响,GPU与CPU之间沟通效率很低,无法满足巨量数据传输处理效率需求,此前英伟达为了解决这个问题,研发了高速通道技术NVLink,但合作伙伴只有较冷门的IBM Power,而市场占有率较大的英特尔和AMD都有自身的加速器,自然也不会加入英伟达的支援阵列。

所以英伟达只能另起炉灶,踏上自研CPU之路,借由Arm架构的特性,Grace可让GPU直接存取系统存储资源,让CPU更好的处理其他工作。未来或许能看见更多Arm架构CPU搭配NVIDIA GPU的组合应用。此举也昭示了将Arm架构应用在AI运算及超算领域确实有其发展机会,同时或将吸引更多伺服器业者开始进行Arm布局,扩大Arm架构在手机、嵌入式以外的应用。

AMD收购赛灵思,补齐FPGA产品线

近日AMD完成了对赛灵思的收购,AMD的CPU和赛灵思的FPGA,未来也将走向CPU+FPGA的异构整合中。因为,这条路英特尔已经趟过,收购了Altera之后,FPGA产品线在英特尔中发挥的不错,2018 年,英特尔宣布将“Skylake”至强SP处理器 Arria 10 FPGA 混合在一个封装中的产品。FPGA在现成CPU 上运行的编程语言和用于实现某些功能或软件堆栈的定制ASIC之间的边界仍然具有吸引力。

总之,收购赛灵思之后,AMD 设计的每个计算设备,无论是单芯片还是封装中的Chiplet集合,都可以在 AMD 认为合适的时候添加一些可编程逻辑。

英特尔向GPU扩展的动作很大,英伟达研究CPU自立自强的决心也很大,气势正旺的AMD有了FPGA也如虎添翼。随着三大厂商逐渐补齐产品线,异构计算或将进入全面爆发。未来,异构计算会越来越多的取代原来通用计算不擅长的部分。

02 国内芯片厂商跟进

不同于国际大厂在各方面实力雄厚,国内厂商难以在短时间内形成如此全的产品线,但是国产芯片厂商现在已经渐渐开始选择通过投资和合作的方式埋下异构的种子。

2021年11月,GPU芯片企业壁仞科技,与IDG资本、字节跳动等共同参与了国产DPU初创企业云脉芯联数亿元的天使轮投资。据壁仞科技创始人、董事长、CEO张文透露,除了DPU之外,从布局整体计算产业出发,壁仞科技正在密切关注国产CPU的最新发展,未来形成CPU+GPU+DPU的全国产系统级解决方案。

日前,DPU芯片厂商云豹智能与AI芯片厂商燧原科技达成了战略合作,共同研发和提供大规模高性能AI算力平台解决方案。基于云豹智能云霄DPU和燧原科技云燧T20率先推出了DataDirectPathStorage解决方案,为AI训练储存访问提供更高效的解决方案。在传统解决方案中,云燧T20访问存储时,需要将数据先搬移到系统内存,再由系统内存搬移到目标设备。而基于DataDirectPath Storage技术,云燧T20可通过DPU直接获得数据,从而绕过系统内存和CPU,让数据访问速度更快,访问延迟更短,系统开销更小。

此外,国内还有异构处理器IP提供商华夏芯,通过自主设计的Unity统一指令集架构和基于此架构的CPU、DSP、GPU、AI专用处理器系列IP与SoC,在提升性能价格比的同时,显著降低计算芯片研发成本和研发复杂度,同时缩短研发周期,减少开发人员工作量和降低开发门槛。据悉,华夏芯的Unity和英特尔的OneAPI都是为了简化编程环境,但不同的是,OneAPI是面向不同体系架构的统一编程环境,Unity是面向不同微架构的统一体系架构和统一编程环境。

03 晶圆厂和封装厂在异构集成上的布局

异构计算的强大只有完备的通用计算芯片产品线还不够,还必须要有先进的异构集成封装技术将其巧妙的封装在一起,才能达到最终提升算力的目的。因此,这几年异构集成也重新定义了封装在芯片产业链中的地位,现在封装起到一个重新架构的作用。

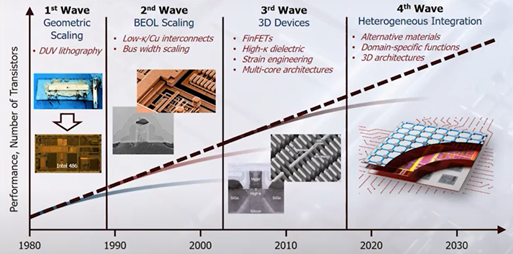

异构集成将是延长摩尔定律的第4波浪潮(图源:ERI summit 2020)

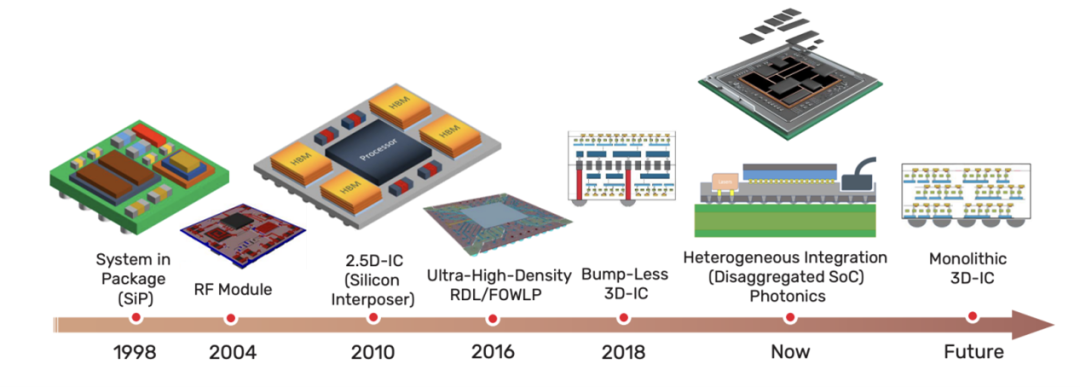

过去,考虑到功耗、性能、成本等因素的影响,芯片的集成首先在单片上进行,例如SoC。但现在摩尔定律逐渐来到极限,在单片上继续微缩,成本效益越发不受控制。而得益于近十年来先进封装与芯片堆叠技术的发展,例如3D堆叠、SiP等,也使得异构集成成为了大幅存在可能。下图显示了先进芯片封装技术的趋势。

先进多芯片(let)封装技术的演进(图源:Cadence)

异构集成主要是将多个不同工艺节点的芯片封装到一个封装内部,这些芯片可以是不同种类、不同制造商、甚至是不同材料(Si/SiC/GaN)、不同工艺节点(如7nm和28nm等搭配),以此来达到增强功能和提高性能。新的封装技术能够将来自不同制造工艺流程的小芯片集成到具有多种功能的单个封装中。

为此,无论是台积电、三星和英特尔这样的晶圆大厂,还是封装厂,都在积极布局异构集成,在半导体后道技术上做好集成的工作。先进封装逐渐成为集成电路芯片成品制造产业的关键工艺技术之一。

三大晶圆厂发力3D先进封装

目前英特尔、三星电子与台积电已具备成熟的2.5D封装经验,如较为人熟知的台积电的CoWos,三星的I-Cube。接下来重点看下3D封装,因为3D封装可以说将异构集成发挥的淋漓尽致。

在3D封装部分,英特尔已量产Foveros技术,其是使用异构堆叠逻辑处理运算,可以把各个逻辑芯片堆叠一起。以往堆叠仅用于存储,现在首度把芯片堆叠从传统的被动硅中介层与堆叠记忆体,扩展到高效能逻辑产品,如CPU、GPU与AI 处理器等。此外,英特尔还研发了三项助于Foveros的技术,分别为Co-EMIB、ODI和MDIO,其中,Co-EMIB 能连接更高的运算性能和能力,并能够让两个或多个Foveros元件互连,设计人员还能够以非常高的频宽和非常低的功耗连接模拟器、存储器和其他模组。ODI技术则为封装中小芯片之间的全方位互连通讯提供了更大的灵活性。顶部芯片可以像EMIB 技术一样与其他小芯片进行通讯,同时还可以像Foveros 技术一样,通过硅通孔(TSV)与下面的底部裸片进行垂直通讯。

近日,英特尔为Aurora 超级计算机提供动力的处理器 Ponte Vecchio,就是一个结合了多个计算、缓存、网络和内存硅片或“小芯片”的封装。封装中的每块tile都是使用不同的工艺技术制成的,这可以说是异构集成的一个鲜明例子。该处理器就使用了Foveros的3D堆叠封装技术和Co-EMIB连接技术。

三星的3D封装技术是X-Cube,其与英特尔的Foveros 3D堆叠技术路线大致相同。目前三星已经完成了3D堆叠SRAM的验证,此外,三星也提供了一项差异化技术,ISC(集成堆叠电容),这一电容应用了已经在三星DRAM产品中获得验证的硅电容结构、材料和工艺,具有1100nF/mm2的电容密度,可以有效提高电源完整性。三星的ISC还提供了多种不同的配置,比如分立型、硅中介层型和多晶圆堆叠型,以满足客户不同的结构需求,ISC预计将在2022年进入量产阶段。

台积电提出了3D多芯片与系统整合芯片(SoIC)的整合方案。SoIC是将不同尺寸、制程技术,以及材料的已知良好裸片直接堆叠在一起。台积电表示,相较于传统使用微凸块的3D集成电路解决方案,SoIC的凸块密度与速度高出数倍,同时大幅减少功耗。此外,台积电也推出了3D Fabric,3DFabric能协助客户将多个逻辑芯片,甚至串联高频宽记忆体(HBM)或异构小芯片,例如模拟、I/O,以及射频模组连结在一起,联合3D SoIC技术能提供更好的灵活性,透过稳固的芯片互连打造出强大的系统。

从上述三大厂商在3D封装的研究也可以看出,三家都各自提供了异构设计的方法和工具,来帮助设计者克服多出来的接口IP或者潜在的功耗增加,以及多芯片互联的问题等等。

封装厂在先进封装上的努力

在异构集成的大势之下,封装厂的作用自然也是重要的一环。在封装领域,我国可谓发展较早,实力相对较强。而系统级封装(System inPackage, SiP)能实现高度集成的微型化系统,整合各种感测器与多样功能的芯片(例如MCU、存储器)等在终端产品之微小空间中,是未来穿戴装置主流封装技术。因此,各家封装厂也在SiP封装上大力布局。

首先是在SiP封装布局已有10年之久的日月光、拿下了苹果的订单后,日月光今年将进入收割元年,而且日月光今年将SiP列为营收中的单独要项。法人表示,日月光SiP目前应用以Wi-Fi整合芯片及指纹辨识芯片为主,产能利用率达满载。预估2022年SiP营收占日月光整体营收比重将达20%以上。

安靠(Amkor)基于衬底的SiP技术在其韩国ATK4光州的*批量制造工厂应用。去年11月底,据报道,Amkor计划在越南Bac Ninh建立*进的智能工厂,新工厂的*阶段将专注于系统级封装 (SiP) 组装和测试解决方案。据Amkor透露,一期建设预计将于 2022 年开始,根据预计的客户产品周期,预计将于 2023 年下半年开始大批量生产。

大陆的封装企业,尤其是中国封测三强(长电、通富、华天)近几年通过自主研发和兼并收购,正在快速积累先进封装技术。例如长电科技旗下长电韩国积极布局高阶SiP封装业务,切入手机和穿戴式装置等终端产品;2016年收购了AMD两家专门从事封装及测试业务子公司的通富微电,也在做SiP的产品,而且公司2021年上半年2.5D/3D封装产品技术已完成立项。

上述这些封装企业主要是针对年产量在10KK左右的SiP封装需求,但除此之外,还有一些专注于细分领域(如工业和医疗等)的异质集成SiP封装厂商,如摩尔精英等,他们主要是解决市场上多样化、小批量的产品设计生产需求。据了解,摩尔精英已经在惠山经济开发区建立自有SiP工厂,所面向的客户主要为年产量1kk左右的产品,摩尔精英SiP一站式服务提供从电路图设计到量产的各个环节。

不过综合来看,IDM与晶圆代工厂商在2.5D、3D等封装技术的发展相对委外半导体封测(OSAT)业者成熟、完整,也具有多年量产经验,所以专业封测厂商不仅要与同业竞争,也要与晶圆代工厂一起竞争。

04 结语

来到2022年,异构计算大战,一触即发。芯片厂商不遗余力的布局CPU、GPU、FPGA、DPU等计算芯片,放出你争我赶的时间轴,代工厂和封装厂也在铆足劲向异构计算的先进封装布局,不止这些厂商,EDA厂商、半导体设备厂商、材料厂商、测试企业等都在为异构计算的来临做准备,异构计算的发展需要全产业链的共同协作,各产业链成熟起来,才能真正迎来大爆发。